Recently I had a chance to chat with Arasan Ganesan, CEO at Arasan Chip Systems in San Jose, CA. Arasan Chip Systems has provided Silicon interface IP and supporting hardware and software to the semiconductor industry for more than 15 years. The headquarters are in San Jose and engineering offices in Bangalore and Tuticorin, India.… Read More

Tag: semiconductor ip

MIPS Warrior Goes Into Battle

You are probably aware that Imagination Technologies, perhaps most well known for creating the GPU that is in the iPhone and iPad, acquired MIPS, which was originally a spinout from Silicon Graphics and licenses a line of general purpose microprocessors.

MIPS considers that they have a purer implementation of the RISC philosophy… Read More

Physical IP Update at DAC

Last year at DAC I visited this little-known physical IP company called DXCorr, so I decided to visit them again this year and get an update.… Read More

Should You Buy All Aspects of Your IP From a Single Supplier?

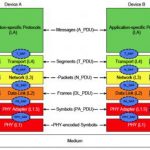

Interface IP typically consists of multiple layers, most importantly a PHY (level 1) analog (or mixed signal) block that handles the interface to the outside world and a number of levels of digital controllers. The interfaces between all these levels, especially between the PHY and the controller, is often defined by the interface… Read More

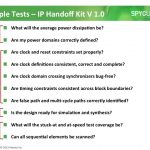

DAC IP Workshop: Are You Ready For Quality Control?

On Sunday I attended an IP workshop which was presented by TSMC, Atrenta, Sonics and IPextreme. It turns out that the leitmotiv of the afternoon was SpyGlass.

Dan Kochpatcharin of TSMC was first up and gave a little bit of history of the company. They built up their capacity over the years, as I’ve written about before, and last… Read More

CDN Live 2013 in Munich: what’s the next acquisition? Evatronix!

It was definitely a good idea to go to Munich to listen to the keynote talk from Lip-Bu Tan. Did I learned in direct live the name of the next acquisition from Cadence in 2013, after Tensilica and Cosmic Circuits? Yes and the winner is… Evatronix! And cadence as well as Evatronix is enjoying more than 600 customers worldwide, thanks … Read More

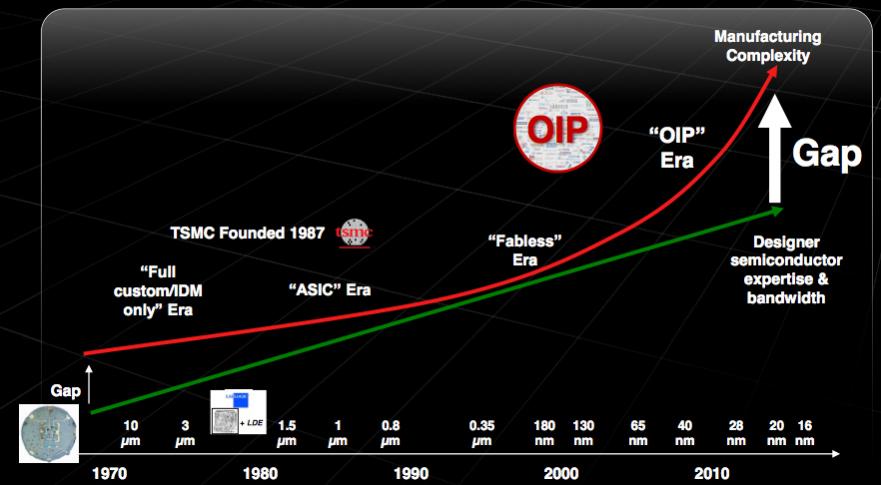

Fabless to OIP

Suk Lee drew the short straw at the TSMC Symposium yesterday, with the 5pm slot. Not only late in the day but between all the attendees and free beer. The morning sessions had been standing room only, with several hundred standees (as they call them on muni around here, but isn’t a standee really someone being stood on?). But … Read More

TSMC on Collaboration: JIT Ecosystem Development

Cliff Hou of TSMC gave the keynote today at SNUG on Collaborate to Innovate: a Foundry’s Perspective. Starting around 45nm the way that a foundry has to work with its ecosystem fundamentally changed. Up until then, each process generation was similar enough to the previous one, apart obviously from size, that it could be … Read More

Cadence IP Report Card 2013

The challenges of developing IP blocks, integrating them correctly, and hitting the power, performance, area, and time to market requirements of a mobile SoC is a growing problem. At 20nm and 14nm the probability of a chip re-spin due to an error is approaching 50% and we all know how disastrous a re-spin can be, those are not good … Read More

Who Allegedly Broke Tela’s Patents: Is Samsung or Qualcomm the Real Villain?

I recently blogged about the actions filed by Tela Innovations at both the US International Trade Commission (USITC) and in federal district court. Those actions allege that five mobile phone manufacturers -HTC, LG, Motorola Mobility, Pantech, and Nokia – were importing handsets into the US which infringed on seven of… Read More