In 2003, when Open-Silicon was founded there was a growing need for flexible and innovative ways of getting chip designs manufactured. Semiconductor companies, given the alternatives of COT or traditional ASIC, often were looking for more flexibility without the huge investment and risk of going COT. Let’s look at how Open-Silicon… Read More

Tag: semiconductor design

Top Ten Insights on the EDA and Semiconductor Industry

I recently had the opportunity to chat with Anirudh Devgan, senior vice president and general manager at Cadence, who leads the Digital and Signoff Group. We discussed recent product development initiatives at Cadence, and talked about future EDA and semiconductor market opportunities. His insights and comments were keen … Read More

Pathfinding to an Optimal Chip/Package/Board Implementation

A new term has entered the vernacular of electronic design engineering — pathfinding. The complexity of the functionality to be integrated and the myriad of chip, package, and board technologies available make the implementation decision a daunting task. Pathfinding refers to the method by which the design space of technology… Read More

Expanding 3D EM Simulation Access to All

James Clerk Maxwell’s eponymous equations are the basis for simulating electromagnetic wave propagation. In school, EE majors tended to fall into two camps: (a) those that thoroughly enjoyed their fields and waves classes, who liked doing surface integrals, and who were adept at demonstrating the “right hand rule”, and (b) … Read More

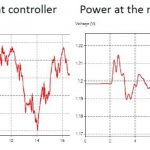

DesignCon 2016 — signal integrity must be power-aware!

DesignCon is a unique conference — its tagline is “Where the Chip meets the Board”. Held each January in Santa Clara, the conference showcases a wealth of new technologies for advanced packaging, printed circuit board fabrication, connectors, cables, and related analysis equipment (e.g, BERT, VNA, scopes). Of specific… Read More

Evaluating the Performance of Design Data Management Software

In the wake of increased global competitiveness and shorter time-to-market windows, there has been a renewed focus by design management on the underlying data management infrastructure of the design teams. An increasing number of systems-on-chip (SoCs) now have some type of analog, digital and/or RF modules, making it imperative… Read More

The Fine Art of Engineering

There’s a small art gallery near the office. It features a new set of paintings by a local artist every two weeks. As I walk by I tend to check out what’s hanging in there. Sometimes I turn up my nose at what I see – a bit too wacky, a bit too abstract, a bit too paint by numbers. Sometimes I walk in to take a closer look but leave the shop empty-handed… Read More

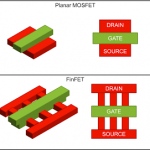

The Death of Moore’s Law

For the last several years, people have predicted the end of Moore’s Law. The reasoning is that there is a limit at which one can’t shrink transistors any further. A reoccurring comment has been “You can’t divide an atom.” I had assumed that its demise would be at the hands of a new paradigm like quantum computing. Now, with Intel’s … Read More

Japan..silent but strong players of semiconductor industry

Japanese stood to be the world leaders during 1980-1990 regime in semiconductor manufacturing[SUP] [2][/SUP]. During my research, I found that Japanese semiconductor firms are very strong leaders in process which gave them a competitive advantage over others. Situation is bit different today, as we have fabless firms taking… Read More

Synopsys on the Future of Custom Layout!

Analog and mixed signal design has received more than their fair share of attention since the mobile revolution and now that FinFETs are in production at the foundries I see that trend continuing. As a result this year there are some interesting things brewing in EDA, especially in the area of Custom Layout.

Innovation in Custom … Read More