These days the verification process starts right when the design process begins, and it keeps going well past the end of the design phase. Simulation is used extensively at every stage of design and can go a long way to help validate a design. However, for many types of designs, especially those that process complex data streams, … Read More

Tag: sce-mi

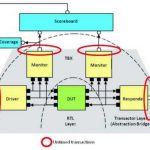

The Rise of Transaction-Based Emulation

One serious challenge to the early promise of accelerating verification through emulation was that, while in theory the emulator could run very fast, options for driving and responding to that fast model were less than ideal. You could use in-circuit emulation (ICE), connecting the emulation to real hardware and allowing you… Read More

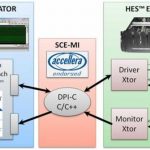

Case study illustrates 171x speed up using SCE-MI

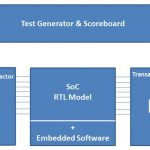

As SoC design size and complexity increases, simulation alone falls farther and farther behind, even with massive cloud farms of compute resources. Hardware acceleration of simulation is becoming a must-have for many teams, but means more than just providing emulation… Read More

Striving for one code base in accelerated testbenches

Teams buy HDL simulation for best bang for the buck. Teams buy hardware emulation for the speed. We’ve talked previously about SCE-MI transactors as a standardized vehicle to connect the two approaches to get the benefits of both in an accelerated testbench – what else should be accounted for?… Read More

Webinar alert – Taking UVM to the FPGA bank

UVM has become a preferred environment for functional verification. Fundamentally, it is a host based software simulation. Is there a way to capture the benefits of UVM with hardware acceleration on an FPGA-based prototyping system? In an upcoming webinar, Doulos CTO John Aynsley answers this with a resounding yes.… Read More

Aldec increasing the return on simulation

Debate rages about which approach is better for SoC design: simulation, or emulation. Simulation proponents point to software saving the need for expensive hardware platforms. Emulation supporters stake their claims on accuracy and the incorporation of real-time I/O. A few years back, some creative types coined the term SEmulation,… Read More

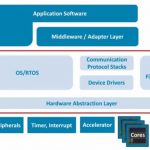

3 reasons to focus on hardware dependent software

Why is software for modern SoCs so blasted expensive to develop? One reason is more software is being developed at the kernel layer – hardware dependent software, or HdS. Application software often assumes the underlying hardware, operating system, communication stacks, and device drivers are stable. For HdS, this flawed assumption… Read More

With SCE-MI, timing really is everything

In one of my favorite movies, Brad Pitt utters the only question that matters in baseball or technology management in the face of uncertainty: “Okay, good. What’s the problem?” Not surprisingly in that scene, as the question circles the table of experts used to doing things the old way, not a single one can answer it correctly in the… Read More