You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

SLiC Library tool dramatically accelerates DTCO for 3nm and beyond

In advanced technology nodes below 10nm, Design and Process Technology development have become increasingly intertwined. In older nodes the traditional technology roll-out was done mostly in a sequential manner with clear geometry scaling targets set by … Read More

EDA companies advertise their physical verification tools, aka DRC (Design Rule Check), mostly in terms of specific engine qualities such as capacity, performance and scalability. But they do not address an equally if not more important aspect: the correctness of the actual design rules.

Put bluntly: It’s not about how… Read More

While some might have expected the exponential growth in design rules number and complexity to cool down a little, it looks as if these are only heating up more. The multiplicity of technology nodes, lithography options, , fundamental technology options (Bulk, FD-SOI, FinFET), different process flavors and specific applications,… Read More

Design rules are at the heart of the interface between the foundry and semiconductor designers, which makes them so critical. Traditionally, design rules and DRC decks have been developed manually with no or little automation. Design rule definitions are written using WORD or other general purpose office tools, and DRC decks… Read More

Design Rule Check (DRC) is the #1 foundry sign-off check. Fabless companies receive the DRC deck from the foundry; it’s a file comprising thousands of commands in a proprietary checker language for a specific DRC tool. In advanced technologies such a deck executes tens of thousands of geometric operations on the physical… Read More

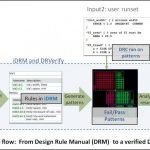

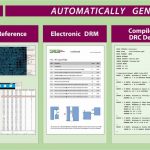

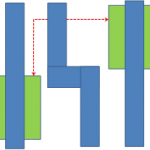

Exactly a year ago Sage Design Automation launched its revolutionary iDRM product, enabling for the first time to graphically capture design rules and compile them into checks automatically – no programming required. Using the graphical design rule editor, users could draw the layout topology that describes the design… Read More

iDRM (integrated design rule manager) from Sage-DA is the world’s first and only design rule compiler. As such it is used to develop and capture design rules graphically, and can be used by non-programmers to quickly capture very complex and shape dependent design rules and immediately generate a check for them. The tool… Read More

This was my 30[SUP]th[/SUP] DAC and the second most memorable. The most memorable was my second DAC (1985) in Las Vegas with my new bride. We had a romantic evening ending with ice cream sundaes at midnight that we still talk about. This year SemiWiki had Dr. Paul McLellan, Dr. Eric Esteve, Daniel Payne, Don Dingee, Randy Smith, and… Read More

This list was compiled by the SemiWiki bloggers highlighting emerging technologies that we have written about and that will be demonstrated at the Design Automation Conference next week. We highly recommend you investigate them further during your time in Austin and please let us know what you think.

Today SemiWiki has more than… Read More

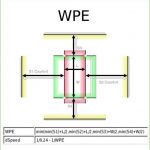

In advanced process technologies, electrical and timing problems due to variability can become a big issue. Due to various processing effects, a circuit performance (both speed and power) is dependent on specific layout attributes and can vary a lot from instance to instance. The accumulated effects can be severe to the point… Read More