On Thursday April 5th the Design and Reuse SoC IP days continues in Santa Clara at the Hyatt Regency (my favorite hangout). SemiWiki is a co-sponsor and I am Chairman of the IP Security Track. More than 400 people have registered thus far and I expect a big turnout, if you look at the program you will see why. You should also know that registration… Read More

Tag: open-silicon

Herb Reiter on the Challenges of 2.5D ASIC SiPs

Years ago my good friend Herb Reiter promoted the importance of 2.5D packaging to anybody and everybody who would listen including myself. Today Herb’s vision is in production and the topic of many papers, webinars, and conferences. According to Herb, and I agree completely, advanced IC packaging is an important technology for… Read More

Open Silicon Year in Review 2017

If you are interested in what types of chips we will see in the coming years always ask an ASIC provider because they know. Companies of all sizes (small-medium-large) use ASIC companies to get their chips out in the least amount of time and at a minimum cost because that is what ASIC companies do.

IP is an important ingredient to the … Read More

New e-Book – Custom SoCs for IoT: Simplified – Available for Free Download

We are fortunate to be living in one of the most amazing and exciting times in the history of our planet. The developments seen in my life time alone have been astounding and we are now on the cusp of yet another inflection point. The world wide web has morphed into the internet of things (IoT), some even call it the internet-of-everything… Read More

Navigating the System-in-a-Package Manufacturing Ecosystem

Being an old ASIC physical design guy, I tend to think of ASICs from a “bond-pads-in” perspective. This week however, I had a very eye-opening discussion with Dan Leung, Director of Packaging and Assembly for Open-Silicon, that totally changed my perspective. While I had been exposed many times to the concept of systems-in-a-package… Read More

ARM TechCon 2017 Preview with Mentor!

Next week is ARM TechCon which is one of my favorite conferences (SemiWiki is an event partner). This year is lucky number thirteen for ARM TechCon and it includes more than sixty hours of sessions plus more than one hundred ARM partners in the exposition. I will be signing free copies of our new book “Custom SoCs for IoT: Simplified”… Read More

Free eBook: Custom SoCs for IoT: Simplified

Two important trends will be discussed in this book: The disruptive nature of the Internet of Things and the use of the ASIC business model by systems companies to get into the chip business.… Read More

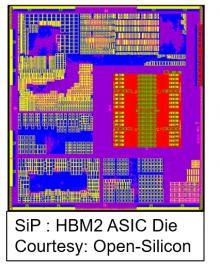

Open Silicon Delivers Silicon-Verified HBM2 IP-Subsystem on TSMC 16nm FF+

Open Silicon hosted a webinar today focusing on their High Bandwidth Memory (HBM) IP-subsystem product offering. Their IP-subsystem is based on the HBM2 standard and includes blocks for the memory controller, PHY and high-speed I/Os, all targeted to TSMC 16nm FF+ process. The IP-subsystem supports the full HBM2 standard with… Read More

High Bandwidth Memory ASIC SiPs for Advanced Products!

When someone says, “2.5D packaging” my first thought is TSMC and my second thought is Herb Reiter. Herb has more than 40 years of semiconductor experience and he has been a tireless promoter of 2.5D packaging for many years. Herb writes for and works with industry organizations on 2.5D work groups and events at conferences… Read More

Webinar Alert: High Bandwidth Memory ASIC SiPs for HPC and Networking Applications

Calling all ASIC designers working on High-Bandwidth Memory (HBM) access architectures in high-performance computing (HPC), networking, deep learning, virtual reality, gaming, cloud computing and data center applications. You won’t want to miss this upcoming webinar focused on system integration aspects of a HBM2 ASIC… Read More