While Truechip has established itself as a global provider of verification IP (VIP) solutions, they are always on the lookout for strategic IP needs from their customer base. Over the last several years, a solid market for Network-on-Chip (NoC) IP has grown, driven by the need to rapidly move data across a chip. Concurrently, the… Read More

Tag: noc

2D NoC Based FPGAs Valuable for SmartNIC Implementation

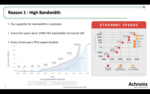

Smart network interface cards (SmartNICs) have proven themselves valuable in improving network efficiency. According to Scott Schweitzer, senior product manager at Achronix, it has been shown that SmartNICs can relieve up to – and perhaps beyond – 30% of the host processor’s loading. SmartNICs started out taking… Read More

Tessent Streaming Scan Network Brings Hierarchical Scan Test into the Modern Age

Remember when you had to use dial up internet or parallel printer cables connected directly to the printer to print something? Well even if you don’t remember these things, you know that now there is a better way. Regrettably, the prevalent methods used for hierarchical Design for Test (DFT) still look at lot like this – SoC level … Read More

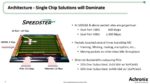

Five Reasons Why a High Performance Reconfigurable SmartNIC Demands a 2D NoC

As part of their webinar series, SemiWiki hosted one in June with the title “Five Reasons Why a High Performance Reconfigurable SmartNIC Demands a 2D NoC.” The talk by given by Scott Schweitzer, Sr. Manager, Product Planning at Achronix. Scott is a lifelong technology evangelist and focuses on recognizing technology trends and… Read More

More Tales from the NoC Trenches

Science texts like to present the evolution of knowledge as step-function transitions, from ignorance to wisdom. We used to think the sun revolved around the earth. Then Galileo appeared, and we instantly realized that the earth revolves around the sun. But reality is always messier, as Galileo understood all too well. The transition… Read More

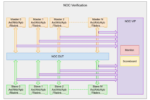

Webinar: Challenges in creating large High Performance Compute SoCs in advanced geometries

When we think about Compute and AI SoCs, we often focus on the huge numbers of calculations being carried out every second, and the ingenious IPs that are able to reach such high levels of performance. However, there also exists a significant challenge in keeping the vast quantities of data flowing around the chip which is solved … Read More

Achronix Next-Gen FPGAs Now Shipping

Earlier in April, Achronix made a product announcement with the headline “Achronix Now Shipping Industry’s Highest Performance Speedster7t FPGA Devices.” The press release drew attention to the fact that the 7nm Speedster®7t AC7t1500 FPGAs have started shipping to customers ahead of schedule. In the complex product world… Read More

Arteris IP Contributes to Major MPSoC Text

You might have heard of the Multicore and Multiprocessor SoC (MPSoC) Forum sponsored by IEEE and other industry associations and companies. This group of top-notch academic and industry technical leaders gets together once a year to talk about hardware and software architecture and applications for multicore and multiprocessor… Read More

SoC Integration – Predictable, Repeatable, Scalable

On its face System-on-chip (SoC) integration doesn’t seem so hard. You gather and configure all the intellectual properties (IPs) you’re going to need, then stitch them together. Something you could delegate to new college hires, maybe? But it isn’t that simple. What makes SoC integration challenging is that there are so many… Read More

CEO interview: Graham Curren of Sondrel

It has been my pleasure to interview Graham Curren, CEO of Sondrel. A veteran of the Electronics Design industry, he founded Sondrel in 2002 to provide digital ASIC designs.

How did you aim to differentiate Sondrel when you started?

My view of the market was that there were a lot of small design companies and also huge in-house design… Read More