One of the unsung heroes of our digital world is the modest voltage converter. Batteries and wired power sources rarely match up with the supply needs for advanced ICs. Leading edge ICs have multiple voltage domains and very often, as in the case of processors, use dynamic voltage scaling to help conserve power. Looking at where … Read More

Tag: mentor

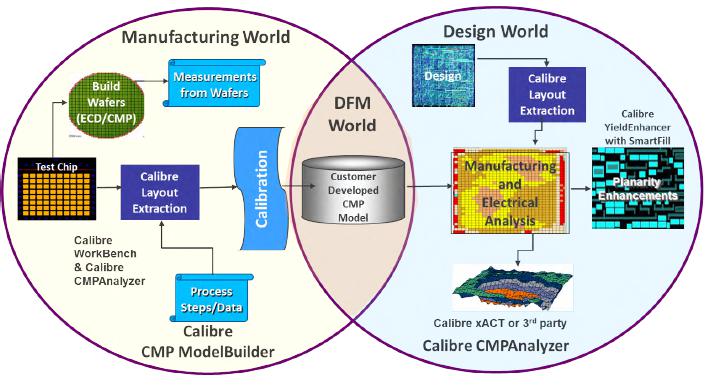

Tackling Manufacturing Errors Early with CMP Simulation

CMP (Chemical Mechanical Planarization or also known as Chemical Mechanical Polishing) is a wafer fabrication step applied generally after a chemical deposition –intended to smoothen and to flatten (planarize) wafer surfaces with the combination of chemical and mechanical forces. Developed at IBM and since its introduction… Read More

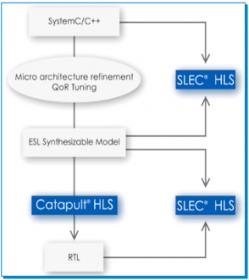

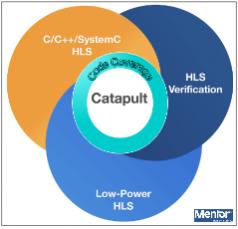

Sequential Equivalency Checks in HLS

Higher level synthesis (HLS) of an IP block involves taking its high-level design specification –usually captured in SystemC or C++, synthesizes and generates its RTL equivalent. HLS provides a faster convergence path to design code stability, promotes design reuse and lowers front-end design inception cost.

HLS and Mentor… Read More

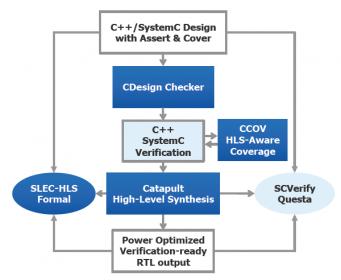

Catapult Design Checker Finds Coding Errors Before High Level Synthesis

In a recent whitepaper Gagandeep Singh, Director of Engineering at Mentor, a Siemens Business outlines a flow using Catapult Design Checker that helps in early detection of coding errors as many companies are turning to High-Level Synthesis (HLS) methodology. This requires that high -level C++ models are correct, that ambiguities… Read More

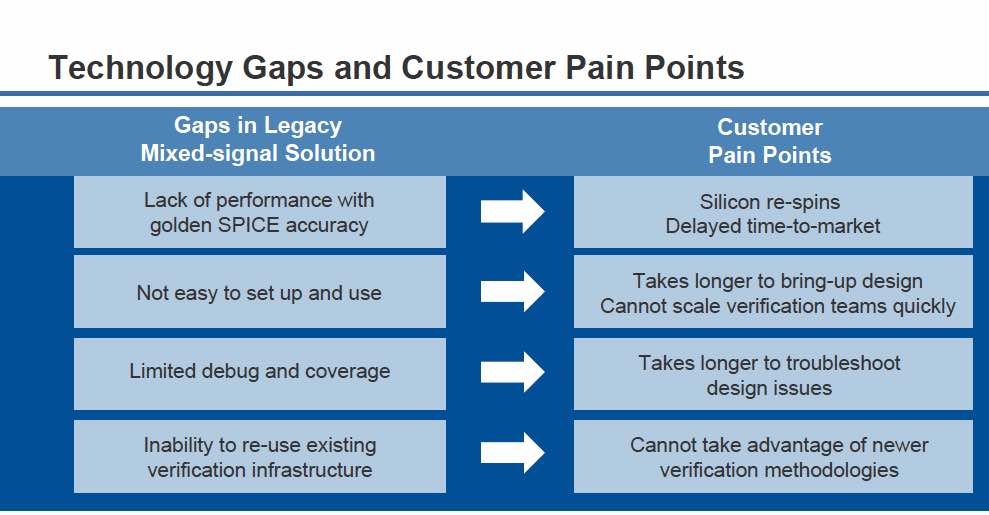

Mentor’s Symphony in Tune with AMS Designer Needs

Mixed signal simulation is a very hot topic these days. In modern designs, it is harder to draw a line between the analog and digital and work with them independently. Analog blocks are showing up everywhere. Even in what would have qualified as a digital design a few years ago, now designers need to look at things like PLLs, IOs and … Read More

Mentor’s Busy ITC and Major Test Product Updates

In conjunction with the 2018 International Test Conference, Mentor has several interesting test announcements. They also have a busy round of technical activities, including a number of technical papers, presentations, tutorials and a poster from a major customer about using Mentor. I’d like to touch on the two product related… Read More

Parasitic Extraction for Advanced Node and 3D-IC Designs

Technology scaling has made positive impacts on device performance, while creating challenges on the interconnects and the fidelity of its manufactured shapes. The process dimension scaling has significantly increased metal and via resistance for advanced nodes 7nm and onward, as shown in figures 1a,1b. Similar to a fancy… Read More

EDA Cost and Pricing

This is the nineteenth in the series of “20 Questions with Wally Rhines”

When I moved from the semiconductor industry to Mentor, I expected most of my technology and business experience to apply similarly in EDA software. To some extent, that was correct. But there was a fundamental difference that required a change… Read More

Closing Coverage in HLS

Coverage is a common metric with many manifestation. During the ‘90s, both fault and test coverage were mainstream DFT (Design For Testability) terminologies used to indicate the percentage of a design being observable or tested. Its pervasive use was then spilled over into other design segments such as code coverage, formal… Read More

Beyond DRC and LVS, why Reliability Verification is used by Foundries

Reliability of ICs isn’t a new thing, because back in 1980 I was investigating why a DRAM chip using 6um technology was having yield loss due to electromigration effects. I recall looking through a microscope at a DRAM layout and slowly ramping up the Vdd level then suddenly the shiny aluminum interconnect started to change… Read More