The use of silicon interposers is growing. Several years ago Xilinx broke new ground by employing interposers in their Virtex®-7 H580T FPGA. Last August Samsung announced what they say is the first DDR4 module to use 3D TSV’s for enterprise servers. Their 64GB double data rate-4 modules will be used for high end computing where … Read More

Tag: mentor

Open Source Software Platform Fuels Automotive Innovation

These days, most of the innovative concepts in our cars are driven by electronics; not only infotainment systems, but also instrument clusters, safety systems including ADAS (Advanced Driver Assistance Systems), information displays, night vision, airbags, backup camera, stability control, and so on. The upcoming connected… Read More

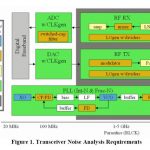

Full Spectrum Analog FastSPICE Useful for RF Designs on Bulk CMOS

It has been about a year since the acquisition of Berkeley Design Automation by Mentor Graphics. Berkeley was doing quite well in the somewhat crowded SPICE simulator market. In many respects they broke new ground for high speed and accurate SPICE simulators. Since the acquisition we know that former Berkeley executives are now… Read More

Mentor 2014 Results

Yesterday Mentor announced their quarterly results. Since their financial year is not aligned with the calendar year, this was also the end of their fiscal 2015. The quarter was an all-time record with revenues of $439M and (non-GAAP) EPS of $1.09. The year was also an all-time record with revenues of $1.24B and EPS of $1.77. Half… Read More

MEMS Require 3D Field Solver for Accurate Cap Values

MEMS devices have become extremely important and common. Freescale last year reported its combined MEMS shipments exceeded 2 billion units. If we just examine how many accelerometers we each probably own today, it is easy to see why the market for these products is growing so rapidly. The first and most obvious device is our cell… Read More

UVM Debugging Made Easy & Productive in Questa

As design complexity and size is increasing, SoC verification has become one of the most difficult and time consuming tasks in the design closure.UVM (Universal Verification Methodology, an accellera initiative) is one of the best verification methodologies that support common language, coherent strategy, clarity and transparency… Read More

Tracing Insight into Advanced Multicore Systems

After knowing about the challenges involved in validating multicore systems and domains of system and application level tracing as explained by Don Dingee in his article “Tracing methods to multicore gladness” which is based on the first part of Mentor Embedded multicore whitepaper series, it’s time to take a deeper insight … Read More

Not All RTL Synthesis Approaches are the Same

My first experience with logic synthesis was at Silicon Compilers in the late 1980s using a tool called Genesil. Process technology since that time has moved from 3 um down to 20 nm, so there are new challenges for RTL synthesis. Today you can find logic synthesis tools being offered by the big three in EDA: Synopsys, Cadence, Mentor… Read More

Tracing methods to multicore gladness

Multiple processor cores are now a given in SoCs. Grabbing IP blocks and laying them in a multicore design may be the easy part. While verification is extremely important, it is only the start – obtaining real-world performance depends on the combination of multicore hardware and actual application software. What should engineers… Read More

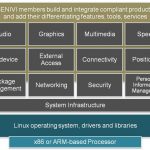

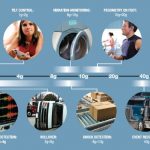

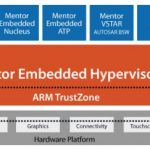

Mentor Moves to Enter IoT Fray

In December I signed up for an IoT “lunch and learn” hosted by Mentor Graphics. There were a number of surprising things about the session. The first and most obvious is that it was really a “breakfast-to-lunch and learn”. Starting at 9AM and going through the end of lunch, it was packed full of ‘learning.’ It was also packed full of … Read More