I have been silently watching STMicroelectronics pursuing FD-SOI technology since quite a few years. FinFET was anyway getting more attention in the semiconductor industry because of several factors involved. But from a technology as well as economic perspective there are many plus points with FD-SOI. I remember my debate,… Read More

Tag: mentor

How Virtualization Makes Network Processor Verification Efficient

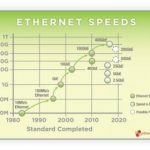

When Ethernet was introduced in 1983 it ran at 10Mbps and mostly relied on hubs and coaxial cable. Twelve years later a faster speed was introduced, running at 100Mbps. Since then we have seen an acceleration of new data rate introductions. According top the Ethernet Alliance, Ethernet could have 12 speeds before 2020, with 6 of … Read More

Nine Cost Considerations to Keep IP Relevant –Part2

In the first part of this article I wrote about four types of costs which must be considered when an IP goes through design differentiation, customization, characterization, and selection and evaluation for acquisition. In this part of the article, I will discuss about the other five types of costs which must be considered to enhance… Read More

Nine Cost Considerations to Keep IP Relevant

It’s about 15 years the concept of IP development and its usage took place. In the recent past the semiconductor industry witnessed start of a large number of IP companies across the globe. However, according to Gary Smith’s presentation before the start of 52[SUP]nd[/SUP] DAC, IP business is expected to remain stagnant for next… Read More

Moving up Verification to Scenario Driven Methodology

Verification complexity and volume has always been on the rise, taking significant amount of time, human, and compute resources. There are multiple techniques such as simulation, emulation, FPGA prototyping, formal verification, post-silicon testing, and so on which gain prominence in different situations and at different… Read More

Mentor 2Q Results

So it was Mentor’s turn yesterday after Synopsys on Wednesday. And yes, it really is the end of their second quarter. They produced some very good results. As Wally opened:The second quarter of fiscal 2016 was one of record for Q2. We substantially exceed our own expectations was revenue of $281.1 million and non-GAAP earnings… Read More

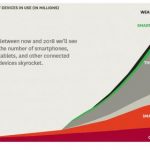

Meeting Demand as Fab Capacity is Stretched Again

Global semiconductor production capacity and its utilization level are key elements of the technology economy. During a panel at DAC in June Mentor Graphics posited that we are entering into a period where leading edge processes will be in high demand and also older nodes are seeing increasing demand due to Internet of Things designs… Read More

What Does Legal Sea Foods Have to Do With EDA?

When I drive down to Silicon Valley I usually listen to podcasts rather than just listen to the radio. One that I especially like is Russ Robert’s EconTalk, which has an hour-long episode every Monday morning on a wide range of different aspects of Economics. Normally he interviews an economist. He has also interviewed the… Read More

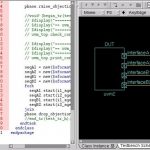

Never Imagined So Easy Class-based Testbench Debugging

When it comes to debugging a design testbench organized in object-oriented style with objects, component hierarchies, macros, transactions and so on, it becomes an onerous, tasteless, and thankless task for RTL verification engineers who generally lag in software expertise. Moreover, class-based debugging tools have lagged… Read More

Power Analysis Needs Shift in Methodology

It’s been the case most of the time that until we hit a bottleneck situation, we do not realize that our focus is not at the right spot. Similar is the case with power analysis at the SoC level. Power has become equally if not more important than the functionality and other parameters of an SoC, and therefore has to be verified earlier … Read More