On Tuesday morning I headed off to the Mentorbooth at DACfor an update on their Custom IC Design and AMS Simulation/Verification tools, Christopher Cone was the presenter. Also in the room were Jay Madiraju, and Mick from Berkeley DA.… Read More

Tag: mentor graphics

Mentor Graphics @ SEMICON West 2014

Mentor is again the most represented EDA company at SEMICON West this year. I strongly advise Cadence and Synopsys to get more involved because EDA may be where electronics begins but semiconductor manufacturing makes all of our hard work come true, absolutely. Paul McLellan, Beth Martin, and I will be blogging live, I hope to see… Read More

Analog FastSPICE Update at DAC

Tuesday night over dinner at DAC I was able to chat with Ravi Subramanian, CEO of Berkeley DA, recently acquired by Mentor Graphics back on March 21st. This acquisition provided Mentor with an Analog FastSPICE circuit simulator to round out its collection of simulators.… Read More

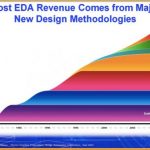

Wally Rhines at #51DAC: EDA Grows From Solving New Problems

Wally Rhines gave the keynote at DAC in 2004. One of the things that he pointed out ten years ago was that EDA revenue for any given market segment is pretty much flat once the initial growth phase has taken place and the market has been established. Incremental EDA revenue only comes from delivering new capabilities. Historically… Read More

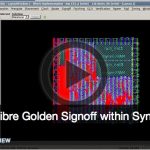

An Update on Calibre at DAC

Even though I live just 7 miles away from the Mentor Graphics corporate office in Oregon, I visited their DAC suite in San Francisco last week to get an update on Calibrefrom Michael White. The Calibre tools are used during IC verification and sign-off by performing DRC (Design Rule Checking) and LVS (Layout Versus Schematic).… Read More

Active Power Management in UPF Using SPICE, VHDL-AMS or Verilog-AMS

My former co-worker, Kenneth Bakalar at Mentor Graphics is an expert in AMS modeling languages and UPFmethodology, so he recently teamed up with Eric Jeandeau to author an interesting white paper: Interpreting UPF for a Mixed-Signal Design Under Test. This white paper is based on a presentation made at DVCon earlier this year.… Read More

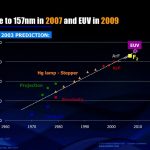

EUV Slips a Year Per Year…Or More

I was at EDPS in Monterey the last couple of days. It is one of the most interesting conferences to attend. Go next year since you already missed it this year. It is not big but the quality of the content is high. Historically the dinner in the middle is in the Monterey Yacht Club and there is a keynote speech. A few years ago it was me but this… Read More

Show Me How To Get Better DRC and LVS Results For My SoC Design

Most IC engineers learn best by hands-on experience when another more experienced person can show us what to do. If you cannot find that experienced person, then the next best thing is a video from an expert. I was surprised to find out that video was so important today that the #2 most viewed web site on the Internet was www.youtube.com… Read More

U2U: Things You Might Not Know About TSMC

At Mentor’s U2U this afternoon I attended a presentation on TSMC’s use of Calibre PERC (it is a programmable electrical rule checker) for qualification of IP in TSMC’s IP9000 program. I’ve written about this before here. Basically IP providers at N20SOC, N16FF, and below are required to use PERC to guarantee… Read More

Sketch Router and auto-assist PCB layout

Archaic tech metaphors abound, stuck in the psyche of users everywhere. We still “dial” numbers, long after the benefit of a short pull area code disappeared. (Humans could dial 1, 2, or 3 a lot faster on a rotary phone, and there were fewer dialpulses for central office switches to decode – thus big cities with more phone traffic like… Read More