Most IC engineers learn best by hands-on experience when another more experienced person can show us what to do. If you cannot find that experienced person, then the next best thing is a video from an expert. I was surprised to find out that video was so important today that the #2 most viewed web site on the Internet was www.youtube.com… Read More

Tag: lvs

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

Best Practices for Using DRC, LVS and Parasitic Extraction – on YouTube

EDA companies produce a wealth of content to help IC engineers get the best out of their tools through several means:

- Reference Manuals

- User Guides

- Tutorials

- Workshops

- Seminars

- Training Classes

- Phone Support

- AE visits

Calibre Update at DAC

Mentor Graphics throws a very nice dinner party at DAC each year for journalists, bloggers and top customers, so this year I spoke with Michael Buehler-Garcia about what’s new with Calibre.

Michael Buehler-Garcia, Mentor Graphics

… Read More

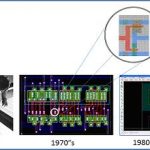

Improving Design Practices for an Image Sensor IDM

With nearly twenty five years in business, Tanner EDA Application Engineers have seen a wide range of support requests. One consistent topic area is around design data management and design reuse. In one recent instance, our customer, an IDM who produces imaging sensors for infrared vision systems, called on Tanners AE team for… Read More

Design-to-Silicon Platform Workshops!

Have you seen the latest design rule manuals? At 28nm and 20nm design sign-off is no longer just DRC and LVS. These basic components of physical verification are being augmented by an expansive set of yield analysis and critical feature identification capabilities, as well as layout enhancements, printability, and performance… Read More

Speeding SoC timing closure

As chips have become larger, one of the more challenging steps is full-chip signoff. Lots of other steps in the design process can work on just a part of the problem, but by definition full-chip signoff has to work on the full chip. But it is not just that chips have got larger, the number of corners that need to be validated has also exploded.… Read More

Aug 25th in Fremont, CA – Hands on Calibre workshop: DRC, LVS, xRC, ERC, DFM

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

DRC Wiki

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

Who Needs a 3D Field Solver for IC Design?

Prevention is Better… Read More