In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More

Tag: jedec

Sigrity Focuses on LPDDR4 Compliance Analysis in 2015 Release

It was back in July of 2012 that the acquisition of Sigrity by Cadence was announced. Although Cadence is a dominant player in both IC and board layout tools, they did not have an electromagnetic (EM) signal integrity solution in their portfolio. This acquisition marks a turning point for the EM/SI sector – tight integration… Read More

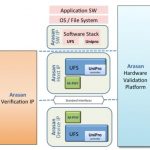

Prototyping Kits to Accelerate IP Development & Integration into SoCs

With growing SoC size, complexity, software and hardware content in it and shrinking time-to-market, the SoC design completion in time has become increasingly dependent on IP which need to be sourced (internally or externally), customized according to the design need and integrated together into the SoC. While IP providers… Read More

Predicting Component Temperature Early in Design

In today’s electronics with multiple functions working together, heat generation is on the rise; sometimes it becomes intolerable. In fact components running at different temperatures can cause timing issues, and very high temperatures can lead to operational issues such as latch-up. An electronic system can contain chips,… Read More

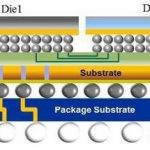

Smart Strategies for Efficient Testing of 3D-ICs

3D-IC has a stack of dies connected and packaged together, and therefore needs new testing strategies other than testing a single die. It’s given that a single defective die can render the whole of 3D-IC unusable, so each die in the stack must be completely and perfectly tested before its entry into that stack. Looking at it from a … Read More

Emerging Trend – Choose DRAM as per Your Design Need

Lately I was studying about new innovations in memory world such as ReRAM and Memristor. As DRAM (although it has become a commodity) has found its extensive use in mobile, PC, tablet and so on, that was an inclination too to know more about. While reviewing Cadence’s offering in memory subsystems, I came across this whitepaperwhich… Read More

Qualcomm JEDEC Mobile Keynote: Memory Bandwidth and Thermal Limits

I went to some of the JEDEC mobile conference a couple of weeks ago. The opening keynote was by Richard Wietfeld of Qualcomm called The Need for Speed.

He emphasized that smartphones are really setting the pace these days in all things mobile and internet. Over 1/3 of access is on smartphones now. Over 4/5 of searches on smartphones… Read More

Is DDR4 a bridge too far?

We’ve gone through two decades where the PC market made the rules for technology. The industry faces a question now: Can a new technology go mainstream without the PC?

By now, you’ve certainly read the news from Cadence on their DDR4 IP for TSMC 28nm. They are claiming a PHY implementation that exceeds the data rates specified for … Read More

Universal Flash Storage: Webinar

There has been a general trend for over a decade now towards the use of very fast serial interfaces instead of wide parallel interfaces. This has been driven by a number of different factors ranging from the lack of pins on an SoC, the difficulty of keeping wide parallel interfaces free of skew, limitations on printed circuit board… Read More

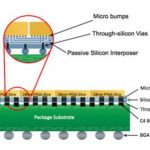

3D-IC Physical Design

When process nodes reached 28 nm and below, it appeared that design density is reaching a saturation point, hitting the limits of Moore’s law. I was of the opinion that the future of microelectronic physical design was limited to 20 and 14 nm being addressed by technological advances such as FinFETs, double patterning, HKMG (High-k… Read More