It’s been quite a while since I talked with Agnisys CEO and founder Anupam Bakshi, when he described their successful first user group meeting. I reached out to him recently to ask what’s new at Agnisys, and his answer was “collaborative specification.” I told him that I wasn’t quite sure what that term meant, and he offered to spend… Read More

Tag: ip-xact

IP-XACT Resurgence, Design Enterprise Catching Up

This standard has been around in one form or another for over ten years and was then arguably ahead of its time. RTL designers were confused: ‘We already have RTL. Why do we need something else?’ I also didn’t get it. Still, the standard plugged ahead among the faithful and found traction among IP vendors. Particularly as a common format… Read More

Small EDA Company with Something New: SoC Compiler

I read the semiconductor press, LinkedIn and social media (Twitter, Facebook) every morning along with an RSS feed that I setup, staying current on everything related to using EDA tools to make the task of SoC design a bit easier for design teams. A recent press release announced a tool called SoC Compiler, so my curiosity was piqued… Read More

SoC Integration – Predictable, Repeatable, Scalable

On its face System-on-chip (SoC) integration doesn’t seem so hard. You gather and configure all the intellectual properties (IPs) you’re going to need, then stitch them together. Something you could delegate to new college hires, maybe? But it isn’t that simple. What makes SoC integration challenging is that there are so many… Read More

Arteris IP folds in Magillem. Perfect for SoC Integrators

Arteris IP and Magillem recently tied the knot, creating a merger of Network-on-Chip (NoC) and related Intellectual Property (IP) with a platform known for IP-XACT based SoC integration and related support. This is interesting to me because I’m familiar with products and people in both companies. I talked to Kurt Shuler, vice… Read More

CEO Interview: Dr. Chouki Aktouf of Defacto

“For more than 18 years, we never stopped innovating at Defacto. We are aware of EDA Mantra “Innovate or Die!”. Innovation is in our DNA, and we never stopped adding new automated capabilities to the SoC design community to help facing complexity and cost challenges, which increase every year.”

Before founding Defacto… Read More

A SoC Design Flow With IP-XACT

Taping out a SoC is never easy. The physical dimensions of the chip often belie the work which has been done to get to the tapeout stage. And it is still not a done deal as the hardware and software development teams await the arrival of the test chip from the foundry to complete the post silicon bring-up and validation. The pressure on… Read More

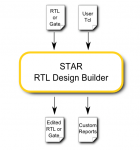

Build Custom SoC Assembly Platforms

I’ve talked with Defacto on and off for several years – Chouki Aktouf (CEO) and Bastien Gratreaux (Marketing). I was in a similar line of business back in Atrenta. Now I’m just enjoying myself, I’ve written a few blogs for them. I’ll confess I wondered why they wouldn’t struggle with the same problems we’d had. Script-driven RTL editing,… Read More

IP-XACT helps you produce exactly what you need in SoC deliverables

If you have ever watched an experienced glass blower, your first thought is that they make it look so easy. I have had the opportunity to blow glass, and I can tell you that it is a constant struggle against temperature, time and muscles to get the glass to do anything like what you want. This is akin to what is required to take the elements… Read More

Dynamic Spectrum Allocation to Help Crowded IoT Airwaves

Radio frequency bandwidth has become a precious commodity, with communications companies paying top dollar for prized pieces of the spectrum. However, many radio bands are not often used efficiently. Many existing radio protocols exchange data on a fixed pair of frequencies, tying up those frequencies for other users. When… Read More