We already know that IP-Xact is extremely useful for managing IP and SOC design specifications, yet it may come as a surprise to learn that it also can be used to form the basis of a power flow too. There are design tools that read UPF to help implement and verify designs, however it can be extremely useful to understand the interplay … Read More

Tag: ip-xact

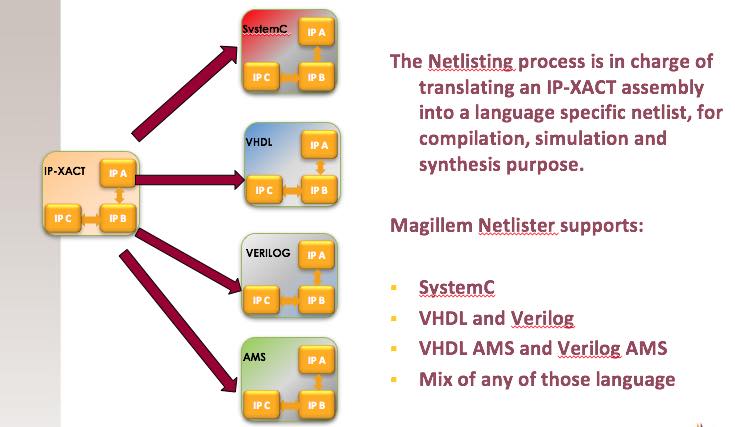

IP-XACT The Answer for IP Reuse

To a lawyer, the term intellectual property means just about anything intangible that has value. However, when you bring that term up in the context of semiconductor design, it means something pretty specific to most people. Yet the implied meaning of the term intellectual property (IP) within the semiconductor field has changed… Read More

Enabling Complex System Design Environment

Deterministic, yet versatile. Robust and integrated, yet user-friendly and easily customizable. Those are some desirable characteristics of an EDA solution as the boundaries of our design optimization, verification and analysis keep shifting. A left shift driven by a time-to-market schedule compression, while the process… Read More

Embracing Architectural Intent

During DVCon 2018 in San Jose, one topic widely covered was the necessity of describing and capturing intent. Defining our design intent up-front is crucial to the overall success of a design implementation. It is not limited to applying a process level intent, such as the use of verification intent with embedded assertions in … Read More

Crystal Bulb: Sharing Design Intelligence

There is a trend among design companies to want to extract more intelligence, from designs in-process and designs past, in support of optimizing total enterprise efficiency. Design automation companies see opportunity in leveraging this interest since they, in various ways, have a handle on at least part of the underlying data.… Read More

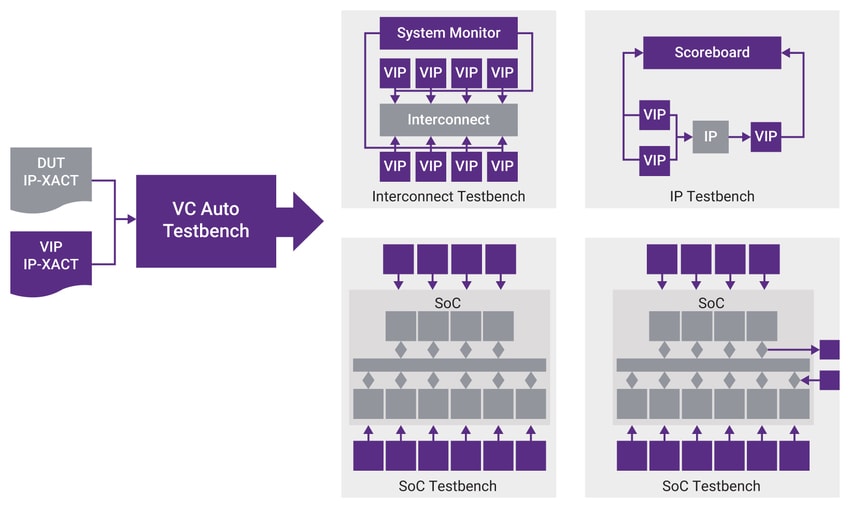

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

Design Data Intelligence

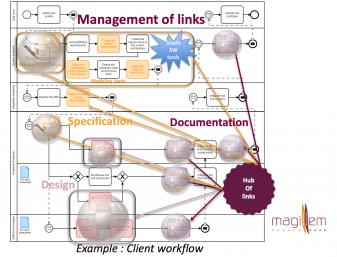

We have an urge to categorize companies, and when our limited perspective is of a company that helps with design, we categorize it as an EDA company. That was my view of Magillem, but I have commented before that my view is changing. I’m now more inclined to see them more as the design equivalent of a business intelligence organization… Read More

Magillem User Group Meeting

Magillem is hosting a user group meeting on October 26th at The Pad in Sunnyvale. User Group meetings are always educational; this one should be especially so for a number of reasons, not least of which is the keynote topic: Expert Systems for Experts.

REGISTER HERE for the meeting in Sunnyvale on October 26[SUP]th[/SUP] from 10:00am… Read More

Virtual Prototyping With Connection to Assembly

Virtual prototyping has become popular both as a way to accelerate software development and to establish a contract between system/software development teams and hardware development and verification. System companies with their tight vertical integration lean naturally to executable contracts to streamline communication… Read More

Simplifying Requirements Tracing

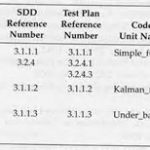

Requirements traceability is a necessary part of any top-down system specification and design when safety or criticality expectations depend on tightly-defined requirements for subsystems. Traceability in this context means being able to trace from initial documented requirements down through specification and datasheet… Read More