There are a lot of articles out right now discussing a possible IPO for Kioxia or sale of the company with Western Digital (WD) and Micron Technology (MT) mentioned as possible acquirers. Kioxia and WD have a partnership for Flash Memory and on March 18th WD gave a presentation on the state of their partnership and what they see as their… Read More

Tag: intel

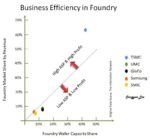

Foundry Fantasy- Deja Vu or IDM 2?

– Intel announced 2 new fabs & New Foundry Services

– Not only do they want to catch TSMC they want to beat them

– It’s a very, very tall order for a company that hasn’t executed

– It will require more than a makeover to get to IDM 2.0

Intel not only wants to catch TSMC but beat them at their own … Read More

Intel Takes Another Shot at the Enticing Foundry Market

Intel made a big splash on March 23, 2021 by doubling down on manufacturing with the creation of Intel Foundry Services (IFS). The big announcement was supported by potential customers such as Qualcomm, Cisco, Ericsson, Google, Amazon, Microsoft, and IBM. With an accompanying $20B investment, the EDA and equipment industries,… Read More

Intel’s IDM 2.0

In January I presented at the ISS conference a comparison of Intel’s, Samsung’s and TSMC’s leading edge offerings. You can read a write-up of my presentation here.

With the problems going on at Intel, that article generated a lot of interest in the investment community, and I have been holding a lot of calls with analysts who are trying… Read More

Micron- Optane runs out of Octane- Bye Bye Lehi- US chip effort takes a hit

– Micron shuts down once promising XPoint

– Lehi Utah fab to be sold off- Had been a $400M drain

– Unique memory couldn’t follow flash down cost/yield curve

– Savings helps Micron but its now just another memory maker

XPoint “Coulda been a contender”

XPoint should have amounted to more… Read More

Podcast EP12: A Close Look at Intel with Stacy Rasgon

Dan takes an in-depth look at Intel with Stacy Rasgon, Managing Director and Senior Analyst, U.S. Semiconductors at Bernstein Research. Stacy is an unusual semiconductor analyst as he holds a Ph.D. in chemical engineering from MIT. His substantial technical knowledge allows for a deep dive on Intel that you will find refreshing… Read More

SPIE 2021 – ASML DUV and EUV Updates

At the SPIE Advanced Lithography Conference held in February, ASML presented the latest information on their Deep Ultraviolet (DUV) and Extreme Ultraviolet (EUV) exposure systems. I recently got to interview Mike Lercel of ASML to discuss the presentations.

DUV

Despite all the attention EUV is getting, most layers are still… Read More

A Review of Clock Generation and Distribution for Off-Chip Interfacing

At the recent ISSCC conference, Mozhgan Mansuri from Intel gave an enlightening (extended) short course presentation on all thing related to clocking, for both wireline and wireless interface design. [1] The presentation was extremely thorough, ranging from a review of basic clocking principles to unique circuit design … Read More

TSMC ISSCC 2021 Keynote Discussion

Now that semiconductor conferences are virtual there are better speakers since they can prerecord and we have the extra time to do a better job of coverage. Even when conferences go live again I think they will also be virtual (hybrid) so our in depth coverage will continue.

ISSCC is one of the conferences we covered live since it’s… Read More

Expert Advice for the New Intel CEO

Intel is a semiconductor legend. Founded on July 18, 1968, the name Intel is short for Integrated Electronics. After leading Silicon Valley, the United Sates, and the world into the era of semiconductors through technical excellence, Intel has hit some challenging times. There has been quite a bit of CEO drama that we will look … Read More