High level synthesis (HLS) seems to have been part of the backdrop of design automation for so long that it seems to be one of those things that nobody notices any more. But it has also crept up on people and gone from interesting technology to keep an eye on to getting genuine adoption. The first commercial product in the space was behavioral… Read More

Tag: hls

NVIDIA and Qualcomm Talk about High Level Synthesis, Samsung on Low Power for Mobile

Since 1978 I’ve seen many trends in the semiconductor design world: transistor-level IC design, gate-level design, RTL coding, High Level Synthesis (HLS) and IP re-use. We’ve witnessed the growth in design productivity enabling chips starting with just thousands of transistor all the way up to billions of transistors… Read More

Verifying the RTL Coming out of a High-Level Synthesis Tool

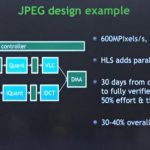

With High-Level Synthesis (HLS) the first benefit that comes to my mind is reduced design time, because coding with C or SystemC is more efficient than low-level RTL code. What I’ve just learned is that there’s another benefit, a reduction in the amount of functional simulation required. One HLS customer was able … Read More

Xilinx’s 16nm UltraScale+ FPGA is Revolutionary

Well a very belated Happy New Year dear reader. I must admit, it has been a very long winter and it has caused the Miller’s to rethink this vital question. “What in the world are we doing living in NY”. So we are moving, and hopefully this is my last ‘real’ winter as we headed down south. To perhaps alleviate some of the winter blues from … Read More

High Level Synthesis Gets Stronger

High Level Synthesis (HLS) tools have been around for at least two decades now, and you may recall that about one year ago Cadence acquired Forte. The whole promise of HLS is to provide more design and verification productivity by raising the design abstraction from RTL code up to SystemC, C or C++ code. With any acquisition it is natural… Read More

Shorten the Learning Curve for High Level Synthesis

When chip designers moved from a gate-level design methodology to coding with RTL there was a learning curve involved, and the same thing happens when you move from RTL to High Level Synthesis (HLS) using C++ or SystemC coding. One great shortcut to this learning curve is the use of pre-defined library functions. I just heard about… Read More

Xilinx the EDA Company

Like you I cannot believe 2015 is upon us. 15 years ago I remember the Y2K panic. I remember watching the news and noticed the liberal media (they were liberal back then too) just waiting for the first fail somewhere. Ended up like Geraldo at the opening of Al Capone’s Vault. Remember that one? As I persist on with this word salad may I … Read More

HLS – Major Improvement through Generations

I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More

Xilinx Boards Make a Great Christmas Gift!

Ok, first thing first, Happy Thanksgiving! For the Miller’s as I get older, it is new traditions as some old ones have passed on. Memories are great and new ones to make. So you know the great debate right?

These poor people working Thanksgiving to sell some tablet or smart phone to save a few bucks. Those that must work, my condolences… Read More

HLS Tools Coming into Limelight!

For about a decade I am looking forward to seeing more of system level design and verification including high level synthesis (HLS), virtual prototyping, and system modeling etc. to come in the main stream of SoC design. Although the progress has been slow, I see it accelerating as more and more tools address the typical pain points… Read More