Audi announced its piloted driving technology at CES 2015. The Audi Prologue includes the Advanced Driver Assistance System Platform (zFAS), co-developed with TTTech. The zFAS board is based on four devices: an Nvidia k1 processor and Infineon Aurix processor, Mobileye’s EyeQ3 for vision processing, and an Altera Cyclone … Read More

Tag: fpga

CCIX shows up in ARM CMN-600 interconnect

All the hubbub about FPGA-accelerated servers prompts a big question about cache coherency. Performance gains from external acceleration hardware can be wiped out if the system CPU cluster is frequently taking hits from cache misses after data is worked on by an accelerator.

ARM’s latest third-generation CoreLink CMN-600 … Read More

Intel Stratix 10 MX FPGA Highlights

These days, FPGAs are fairly complex pieces of silicon. Being that the case, it would take several articles even to put a summary of the features embedded in high-end FPGA devices. Hence, in this article, I will concentrate in just one feature, namely, the new embedded memory blocks of the recently released Intel-Altera Stratix… Read More

Mentor Functional Verification Study 2016

Periodically, Mentor commissions a user/usage survey on Functional Verification, conducted by the Wilson Research Group, then they publish the results to all of us, an act of industry good-citizenship for which I think we owe them a round of thanks. Harry Foster at Mentor is breaking down the report into a series of 15 blogs. He’s… Read More

SoC FPGAs for IoT Edge Computing

One of the reasons for the explosive growth of IoT is that embedded devices with networking capabilities and sensor interfaces are cheap enough to deploy them at a plethora of locations.

However, network bandwidth is limited. Not only that, but also, the latency of the network can be of seconds or minutes. By the time the sensor data… Read More

FPGAs at Deep Machine Learning

The concept of machine learning is not new. Attempts at systems emulating intelligent behavior, like expert systems, go as far back as the early 1980’s. And the very notion of modern Artificial Intelligence has a long history. The name itself was coined at a Dartmouth College conference (1956), but the idea of an “electronic… Read More

Pseudo random generator tutorial in VHDL (Part 3/3)

On the first two chapters of this Tutorial we started with a simple LFSR module and added a test bench. Then, on chapters three and four we upgraded our module with some features and learned to export the test bench data to files.

… Read More

Pseudo random generator tutorial in VHDL (Part 2/3)

In the first part of this tutorialwe started with a simple implementation of an LFSR block (Chapter 1) and its test bench (Chapter 2). Let’s make our code look a bit more professional.

… Read More

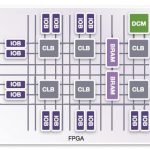

Pseudo random generator tutorial in VHDL (Part 1/3)

In this tutorial we will see how to design a VHDL block. We will start with a very simple block and we will gradually add features to it. We will also simulate it and test its output with Matlab. Over the process we will see:

… Read More

Did My FPGA Just Fail?

Designing DRAMs at Intel back in the 1970s I first learned about Soft Errors and the curious effect of higher failure rates of DRAM chips in Denver, Colorado with a higher altitude than Aloha, OR. With the rapid growth of FPGA-based designs in 2016, we are still asking the same questions about the reliability of our chips used for safety-critical… Read More