Aldec tools and services have long been associated with FPGA designs. As FPGAs have evolved toward more RTL-based designs, the similarities between a modern FPGA verification flow and an ASIC verification flow often leave them looking virtually the same. … Read More

Tag: fpga design

One FPGA synthesis flow for different IP types

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

Updated tool cuts through DO-254 V&V chaos

Audits. The mere mention of the word keeps project managers up at night and sends most designers running. However, in the case of FPGA designs seeking DO-254 compliance, the product doesn’t ship until the audit is complete – there is no avoiding it, or skating around it.… Read More

3 flavors of TMR for FPGA protection

Back in the microprocessor stone age, government procurement agencies fell in love with the idea of radiation hardened parts that might survive catastrophic events. In those days, before rad-hard versions of PowerPC and SPARC arrived, there were few choices for processors in defense and space programs.

One of the first rad-hard… Read More

Dominating FPGA clock domains and CDCs

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

Real FPGAs don’t eat fake test vectors

Vector blasting hardware is as old as digital test methodology itself. In the days of relatively simple combinational and finite state machine logic, a set of vectors aimed broadside at inputs could shake loose most faults with observable outputs. With FPGAs, creating an effective set of artificial test vectors has become a lot… Read More

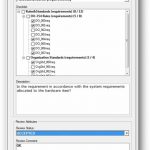

If requirements ask for it, it had better be there

Engineers are known for their attention to detail and precision in thinking, but sometimes still struggle during compliance audits. This is especially true the longer a list of requirements becomes, especially unstructured lists kept in spreadsheets and on Post-It notes.

It gets even more complicated, because in defense circles… Read More

2014: Keep calm, and program gates

I was tempted to call this piece “if you’re not using an FPGA, you’re doing it wrong,” but that didn’t quite capture the whole picture. Social memes aside, the FPGA as we know it is undergoing a serious transformation into a full blown SoC, and 2014 is the year that will usher in one of the biggest changes in the history of embedded design.… Read More

Beyond one FPGA comfort zone

Unless you are a small company with one design team, the chance you have standardized on one FPGA vendor for all your needs, forever and ever, is unlikely. No doubt you probably have a favorite, because of the specific class of part you use most often or the tool you are most familiar with, but I’d bet you use more than one FPGA vendor routinely.… Read More