Last week I sat in on Oski’s latest in a series of “Decoding Formal” sessions. Judging by my first experience, they plan and manage these events very well. Not too long (~3 hours of talks), good food (DishDash), good customer content, a good forward-looking topic and a very entertaining wrap-up talk.… Read More

Tag: formal verification

An InFormal Chat

Any sufficiently advanced technology is indistinguishable from magic, as the saying goes. Which is all very well when the purpose is entertainment or serving the arcane skills of a select priesthood, but it’s not a good way to grow a market. Then you want to dispel the magic aura, make the basic mechanics more accessible to a wider… Read More

Machine Learning – Turning Up the Sizzle in EDA

There’s always a lot of activity in EDA to innovate and refine specialized algorithms in functional modeling, implementation, verification and many other aspects of design automation. But when Google, Facebook, Amazon, IBM and Microsoft are pushing AI, deep learning, Big Data and cloud technologies, it can be hard not to see… Read More

Michael Sanie Plays the Synopsys Verification Variations

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More

Synopsys Software Integrity: Find All the Bugs

A couple of days ago Synopsys announced that they were acquiring Quotium’s product Seeker. This is an interactive application security testing (IAST) product. Synopsys are acquiring the product and the R&D team, not the whole of Quotium. The Seeker solution is a pioneering solution for IAST that helps businesses find high-risk… Read More

OneSpin Launchpad, the App Store for Formal Verification

Formal verification is qualitatively different from most other verification. A simulation can pass or fail. But while formal verification can prove that the circuit is correct, or incorrect, it can also return “not proven” which means either that the algorithms realized that they were not powerful enough to prove… Read More

HLS Tools Coming into Limelight!

For about a decade I am looking forward to seeing more of system level design and verification including high level synthesis (HLS), virtual prototyping, and system modeling etc. to come in the main stream of SoC design. Although the progress has been slow, I see it accelerating as more and more tools address the typical pain points… Read More

How Sonics Uses Jasper Formal Verification

The Jasper part of Cadence announced jointly with Sonics a relationship whereby Sonics uses JasperGold Apps as part of their verification. I talked to Drew Wingard, the CTO, about how they use it.

One way is during the day when their design engineers use Jasper as part of their verification arsenal. Interestingly it is the design… Read More

Cadence Acquires Jasper

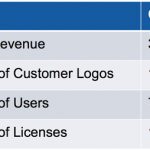

Cadence announced today that it is acquiring Jasper Design Automation for $170M in an all-cash offer. Jasper has $24M in cash so it is really an acquisition for around $145M. i think that is around 4X revenue but I only know rumors about Jasper’s revenue numbers.

All the big 3 already have their own formal technology but the … Read More

Kathryn: "Formal Will Dominate Verification"

At the Jasper Users’ Group meeting, Kathryn presented the state of Jasper. The numbers are impressive. The company has grown at a CAGR of over 35% since 2007, which is 6 times faster than EDA as a whole. They have been profitable at 15-20% EBITDA for 14 consecutive quarters.

Jasper is focused on engaging deeply with a small number… Read More