Ongoing investigations of EUV stochastics [1-3] have allowed us to map combinations of critical dimension (CD) and pitch which are expected to pose a severe risk of stochastic defects impacting the use of EUV lithography. Figure 1 shows a typical set of contours of fixed PNOK (i.e., the probability of a feature being Not OK due… Read More

Tag: euv

Downplaying SMIC – Uplaying TSMC

- KLAC sports solid QTR & Guide- Foundry & Logic drivers

- Management remains dismissive of SMIC embargo

- Execution & financials are solid but macro headwinds remain

- Nice September Quarter

KLA reported revenue of $1.54B and Non GAAP EPS of $3.03 versus street expectations of $1.49B and EPS of $2.77. Guidance is for revenues… Read More

ASML is Strong Because TSMC is Hot!

- ASML has strong quarter lead by great Taiwan and EUV

- EUV “crossed over” DUV as revenue leader- signaling new era

- Taiwan doubles, China grows, Korea weaker, US further behind

ASML hits great numbers

ASML reported revenues of Euro 4B, with income of Euro 2.54EPS, both beating estimates handily. Ten EUV systems were … Read More

Highlights of the TSMC Technology Symposium – Part 1

Recently, TSMC held their 26th annual Technology Symposium, which was conducted virtually for the first time. This article is the first of three that attempts to summarize the highlights of the presentations.

This article focuses on the TSMC process technology roadmap, as described by the following executives:

- Y.J. Mii, SVP,

Fully Self-Aligned 6-Track and 7-Track Cell Process Integration

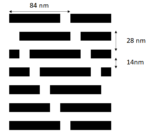

For the 10nm – 5nm nodes, the leading-edge foundries are designing cells which utilize 6 or 7 metal tracks, entailing a wide metal line for every 4 or 5 minimum width lines, respectively (Figure 1).

Figure 1. Left: a 7-track cell. Right: a 6-track cell.

This is a fundamental vulnerability for lithography, as defocus can change… Read More

SEMICON West – Applied Materials Selective Gap Fill Announcement

At SEMICON West, Applied Materials announced a new selective gap fill tool to address the growing resistance issues in interconnect at small dimensions. I had the opportunity to discuss this new tool and the applications for it with Zhebo Chen global product manager in the Metal Deposition Products group at Applied Materials.… Read More

EUV faces Scylla and Charybdis

It is now time for the EUV community to realize they are caught between the proverbial Scylla and Charybdis. In Greek mythology, the two monsters terrorized ships that were unlucky enough to pass between them. By avoiding one, you approached the other.

S for Scylla, or Stochastics

Scylla was a former beautiful nymph turned into

Application-Specific Lithography: a 28 nm Pitch DRAM Active Area

In the recent DRAM jargon, “1X”, “1Y”, “1Z”, etc. have been used to express all the sub-20 nm process generations. It is almost possible now to match them to real numbers which are roughly the half-pitch of the DRAM active area, such as 1X=18, 1Y ~ 17, etc. At this rate, 14 nm is somewhere around

ASML More Covid Concerns and Impact

- Covid related Revenue Rec causes rev/EPS miss

- Sharp order drop reflects H2 industry uncertainty

- EUV remains solid- Memory/Logic mix is better

Results were in line after correcting Covid Caused Revenue Rec issue-

ASML reported revenues of Euro3.3B and EPS of Euro1.79 as revenues from two EUV systems was not recognized, due to … Read More

Application-Specific Lithography: The 5nm 6-Track Cell

An update is now available here: Application-Specific Lithography: Patterning 5nm 5.5-Track Metal by DUV

The 5nm foundry (e.g., TSMC) node may see the introduction of 6-track cells (two double-width rails plus four minimum-width dense lines) with a minimum metal pitch in the neighborhood of 30 nm. IMEC had studied a representative… Read More