Do we ever imagine what kind of severe challenges mission critical unmanned systems in air, land and underwater face? They are limited in space and size; have to be light in weight, flexible in different types of operations and at the same time rugged enough to work in extreme climatic conditions. That’s not enough; amidst these … Read More

Tag: esd

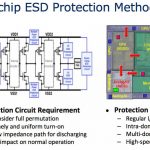

Full Chip ESD Sign-off – Necessary

As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More

Reliability sign-off has several aspects – One Solution

Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

Power and Reliability Sign-off – A must, but how?

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

Robust Reliability Verification: Beyond Traditional Tools and Techniques

Robust Reliability Verification: Beyond Traditional Tools

by Matthew Hogan, Mentor Graphics

At all process nodes, countless hours are diligently expended to ensure that our integrated circuit (IC) designs will function in the way we intended, can be manufactured with satisfactory yields, and are delivered in a timely fashion… Read More

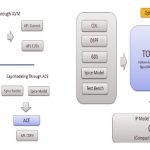

Layout-based ESD Check Methodology with Fast, Full-chip Static and Macro-level Dynamic

Nvidia designs some of the most powerful graphics chips and systems in the world, so I’m always eager to learn more about their IC design methodology. This week I’ve had the chance to talk with Ting Ku, Director of Engineering at Nvidia about his DAC talkin the Apache booth in exactly two weeks from today. Registration… Read More

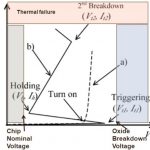

ESD – Key issue for IC reliability, how to prevent?

It’s a common electrical rule that when large amount of charge gets accumulated, it tries to break any of its surrounding isolation. Although it wouldn’t have been prominent in 1980s or 90s, protection for ICs from such damaging effects is a must, specifically in large mixed-signal designs of today, working at different voltages… Read More

First Time, Every Time

While this iconic advertising phrase was first used to describe the ink reliability of a ballpoint pen, it perfectly summarizes the average consumer’s attitude toward automobile reliability as well. We don’t really care how it’s done, as long as everything in our car works first time, every time. Even when that includes heated… Read More

ESD Check Methodology

In Pune at the start of the month, Norman Chang, Ting-Sheng Ku, Jai Pollayil of Apache/Ansys and NVIDIA presented and ESD check methodologywith Fast Full-chip Static and Macro-level Dynamic Solutions . ESD stands for Elecro-Static Discharge and is basically injecting very high static voltages (think how your hand gets charged… Read More

Automating Complex Circuit Checking Tasks

By Hend Wagieh, Mentor Graphics

At advanced IC technology nodes, circuit designers are now encountering problems such as reduced voltage supply headroom, increased wiring parasitic resistance (Rp) and capacitance (Cp), more restrictive electromigration (EM) rules, latch-up, and electrostatic discharge (ESD) damage,… Read More