Electrical Overstress (EOS) and Electrostatic Discharge (ESD) account for most of the field failures observed in the electronics industry. Although EOS and ESD damage can at times look quite similar to each other, the source each and the solution can be quite different. Therefore, it is important to be able to distinguish between… Read More

These failings aren’t just a cross we humans bear; they’re also a concern for chips, particularly in electrical over-stress (EOS) and aging of the circuitry. Such concerns are not new, but they are taking on new urgency given the high reliability and long lifetime expectations we have for safety-critical components in cars and… Read More

Design process retargeting is acommon recurrence based on scaling orBOM(Bill-Of-Material) cost improvement needs. This occursnot only with the availability of foundry process refresh to a more advanced node,but also to any new derivative process node tailored towards matching design complexity, power profile or reliability… Read More

Do not lose sleep worrying that your integrated circuits might fail during EOS/ESD events. Join us for the 38th annual EOS/ESD Symposium in Anaheim, CA in September. Experts on the field will address the latest research on EOS and ESD in the rapidly changing world of electronics.

As electronics continue to become commonplace in… Read More

Last year, about 40% of new smartphones included Near Field Communication (NFC). Analysts predict that by 2017 there will be 1 billion NFC enabled phones. Clearly, the use of NFC is ramping up because it can simplify aspects as diverse as communication, secure payments, user authentication, and retail loyalty programs for instance.… Read More

Almost anyone that is active in IC design will be “in touch” with Electrostatic Discharge (ESD) at some time (pun intended). Preventing ESD related IC failures remains something like black magic—at least it’s easy to get that feeling when you are trying to debug ESD failures. I/O and ESD layouts that resulted in excellent robustness… Read More

In this age of electronics, especially with so many different types of human held devices and more upcoming wearable devices, it’s utmost important to protect the massive circuitry inside those tiny parts in the devices from ESD related failures. The protection needs to happen at all stages – cells inside the chips, package… Read More

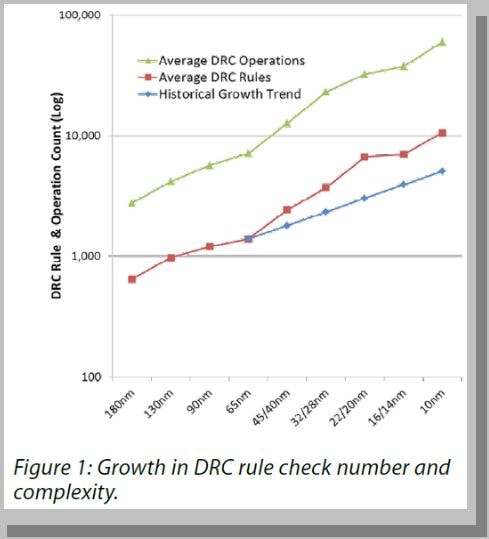

Robust Reliability Verification: Beyond Traditional Tools

by Matthew Hogan, Mentor Graphics

At all process nodes, countless hours are diligently expended to ensure that our integrated circuit (IC) designs will function in the way we intended, can be manufactured with satisfactory yields, and are delivered in a timely fashion… Read More