You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Jasper User Groupby Paul McLellan on 09-25-2012 at 1:19 pmCategories: EDA

The Jasper User Group meeting has been announced. It will take place on November 12th and 13th. As last year, it will be at the Cypress Hotel at 10050 De Anza Boulevard in Cupertino. The user group meeting is free for qualified Jasper customers.

Topics to be covered are, of course, all things verification:

- SoC subsystems verification

…

Read More

You are cordially invited to register to attend the CEVA DSP Technology Symposium Series 2012, which will take place in Taiwan, October 16th, China, October 18th and Israel, November 1st.

CEVA’s industry-leading experts and engineers will present a full day of lectures and seminars where you will learn about the latest technological… Read More

On Wednesday this week Ansys/Ansoft/Apache are presenting a new webinar Chip Aware System Design. It is presented by Dr Steven Gary Pytel Jr of the Ansoft part of Ansys, and Matt Elmore of the Apache subsidiary. The topics that will be covered include:

- Power Delivery Network (PDN) design requirements

- ABCD Matrix theory

- SYZ Matrix

…

Read More

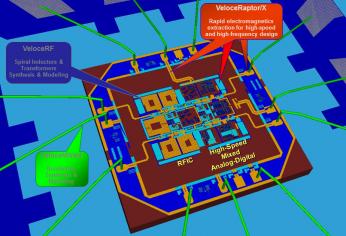

As I have mentioned before, you can tell al lot about a company by their CEO. The previous trip I made to Taiwan was with Helic co-founder and CEO Dr. Yorgos Koutsoyannopoulos. One of the benefits of my job is I get to spend time with some very interesting people from around the world and this was no exception.

Prior to founding Helic, … Read More

Yesterday I attended some of the Cadence mixed-signal technology summit. The day ended with a panel session on Are We Closing the Gap Yet in Mixed-signal Design? Richard Goering moderated. The panelists were all mixed signal experts:

- Nayaz Khan of Maxim

- Nishant Shah of Broadcom

- Shiv Sikand of IC Manage

- Bill Meier of Texas Instruments

…

Read More

Atrenta Wins Goldby Paul McLellan on 09-21-2012 at 6:16 pmCategories: EDA

What is the most read article on design on EE Times website? Brian Bailey has an article up running through the top 10. It turns out that the #1 article is Understanding Clock Domain Issues by Saurabh Verma and Ashima S. Dabare of Atrenta. It actually had more than double the views of the second place paper. Checking clock domain crossing… Read More

In this tough economy you may find yourself displaced and looking for the next opportunity. If you’d like to add some new EDA tool skills, then check out what EMA Design Automation is offering with free Cadence OrCAD training.… Read More

Synopsys announced today that they had completed the two main hurdles to acquiring SpringSoft. Remember, SpringSoft is actually a public Taiwanese company so has to fall in line with Taiwanese rules. The first hurdle is that they have obtained regulatory approval in Taiwan for the acquisition (roughly equivalent to FTC approval… Read More

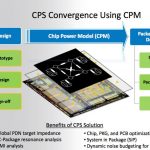

Aveek Sarkar presented a webinar on chip-package-system (CPS) earlier this summer. One of the big challenges with low-power electronic systems is that the performance, power and price goals are mutually conflicting. It’s like the old joke about “pick any 2”. But for a real system all need to be optimized. … Read More

Samsung Invests in Carbonby Paul McLellan on 09-12-2012 at 10:00 amCategories: EDA

I’ve talked before about how venture capitalists will no longer invest in EDA companies since the prospect for a huge return just isn’t there any more. By big return I mean an acquisition at hundreds of millions of dollars, like SPC, CCR, Ambit, Cadmos, Simplex. But we all know that chips cannot be designed without software… Read More