Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

Tag: eda

Increase Your Chip Reliability with iROC Tech

As we have moved towards extremely low process nodes with very high chip density, the cost of mask preparation also has become exorbitantly high. It has become essential to know about the failure rates and mitigate the same at the design time before chip fabrication, and also to make sure about chip reliability over time as it is constantly… Read More

Hardware Assisted Verification

On the Tuesday of DAC I moderated a panel session on Hardware Assisted Verification in 10 Years: More Need, More Speed. Although this topic obviously could include FPGA-based prototyping, in fact we spent pretty much the whole time talking about emulation. Gary Smith, on Sunday night, actually set up things by pointing out that… Read More

First FinFETs Manufactured at #50DAC!

This was my 30[SUP]th[/SUP] DAC and the second most memorable. The most memorable was my second DAC (1985) in Las Vegas with my new bride. We had a romantic evening ending with ice cream sundaes at midnight that we still talk about. This year SemiWiki had Dr. Paul McLellan, Dr. Eric Esteve, Daniel Payne, Don Dingee, Randy Smith, and… Read More

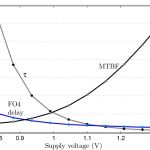

Metastability and Fatal System Errors

Metastability is an inescapable phenomenon in digital electronic systems. This phenomenon has been known to cause fatal system errors for half a century. Over the years, designers have used convenient rules of thumb for designing synchronizers to mitigate it. However, as digital circuits have become more complex, smaller … Read More

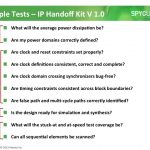

DAC IP Workshop: Are You Ready For Quality Control?

On Sunday I attended an IP workshop which was presented by TSMC, Atrenta, Sonics and IPextreme. It turns out that the leitmotiv of the afternoon was SpyGlass.

Dan Kochpatcharin of TSMC was first up and gave a little bit of history of the company. They built up their capacity over the years, as I’ve written about before, and last… Read More

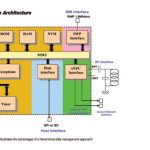

Hierarchical Design Management – A Must

Considering the technological progress, economical pressure, increased outsourcing and IP re-use, semiconductor industry is one of the most challenged industry today. Very frequently products get outdated leading to new development cycles. It becomes very difficult and costly to build the whole scheme of data foundation… Read More

DAC: Tempus Lunch

I had time for lunch on Monday. That is to say, there was a Cadence panel session about Has Timing Signoff Innovation has become and Oxymoron? What Happened and How Do We Fix It?

The moderator was Brian Fuller, lately of EE Times but now Editor-in-Chief at Cadence (I’m not sure quite what it means either). On the panel were Dipesh… Read More

DAC: Wally’s Vision

One new feature at DAC this year is that several of the keynotes are preceded by a ten minute vision of the future from one of the EDA CEOs. Today it was Wally Rhines’s turn. Wally is CEO of Mentor Graphics. He titled his talk Changing the World Through EDA. Since EDA as we know it started in the late 1970s, the number of transistors… Read More

DAC: Gary Smith: Don’t Give Away Your Models

As is now traditional, Gary Smith kicked off DAC proper (there were workshops earlier and some co-located conferences started days before). He started by dismissing the idea that it costs $170M to do an SoC design.

In fact he looked at 3 different cases. Firstly, the completely unconstrained design. Well, no design is completely… Read More