You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

GenApSys is a biotech company developing proprietary DNA sequencing technology. As part of that they develop their own custom sequencing chips. These have an analog component and like many people they use the Cadence Virtuoso analog design environment for this.

I talked to Hamid Rategh who is GenApSys’s VP engineering.… Read More

The Funnest Bugby Paul McLellan on 08-06-2013 at 12:13 amCategories: General

We all have a funnest bug we’ve been involved with. I don’t think ‘funnest’ is actually a word but when my kids used to use the word ‘funner’ I didn’t have a good argument as to why it wasn’t a word, it just seemed a word I’d never heard. In fact I have no idea what the rules are… Read More

Gary Smith did a nice write-up on the current state of electronics media. It’s posted on his Gary Smith EDAwebsite. Traditional media certainly is in transition and there is more change to come, definitely. Gary lists me as one of the heroes carrying the flag which is very nice of him to say. In reality though, he missed Paul … Read More

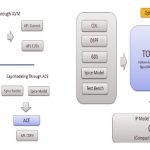

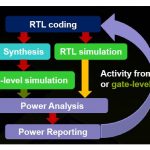

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

This week, I had a nice opportunity meeting Charu Puri, Corporate Marketing and Sushil Gupta, V.P. & Managing Director at Atrenta, Noida. Well, I know Sushil since 1990s; in fact, he was my manager at one point of time during my job earlier than Cadence. He leads this large R&D development centre, consisting about 200 people… Read More

Metastability is a critical SoC failure mode that occurs at the interface between clocked and clockless systems. It’s a risk that must be carefully managed as the industry moves to increasingly dense designs at 28nm and below. Blendics is an emerging technology company that I have been working with recently, their MetaACE… Read More

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

Atrenta today announced Dr Ajith Pasqual, who is the Head of the Department of Electronic & Telecommunication Engineering at the University of Moratuwa in Sri Lanka (which used to be known as Ceylon) has joined Atrenta’s technical advisory board (TAB). OK, academics join EDA company’s TABs all the time so that’s… Read More

It’s a classic and creative example of design and EDA tool community getting together, exploiting tool capabilities and developing flows which add value to all stake holders including the end consumer. We know power has become extremely important for battery life in smart phones, high performance servers, workstations, notebooks… Read More

Part 1

VLSI’s business grew healthily but it never threw off enough cash to fund all the investment required for process technology development and capital investment for a next generation fab. They made a strategic partnership with Hitachi covering both 1um process technology and a significant investment, which meant that … Read More