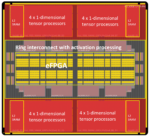

DSP and AI are generally considered separate disciplines with different application solutions. In their early stages (before programmable processors), DSP implementations were discrete, built around a digital multiplier-accumulator (MAC). AI inference implementations also build on a MAC as their primitive. If the interconnect… Read More

Tag: dsp core

CEVA Showcasing Image Processor at MWC Barcelona

Cameras are becoming ubiquitous thanks to a new wave of applications that span GoPro for sports, smart glass for the Internet eyewear, ADAS for car safety, and more. However, while these cameras boast an increasing amount of megapixels to enhance the quality of vision, what they increasingly need is more processing power to analyze… Read More

Winning the IoT protocol battle with DSP

There are too many IoT protocols. Way too many. Anyone who says one single protocol will be the winner from end-to-end in all IoT applications and markets is smoking something. Software defined, multi-protocol gateways are the only hope on the IoT – and DSP cores enable this strategy.… Read More

One Breath, One Milliwatt

To understand how challenging it is to successfully implement Always-on Technology, consider doing any kind of sport while holding your breath. Sounds crazy? There’s actually one sport in which participants do just that – freediving. So what does freediving have to do with always-on technology? Quite a few things apparently.… Read More

I’ll be with you in a second

One aspect of always-on is power conservation, being able to respond to events without having a device constantly in full-power mode. This month, the announcement of the Amazon Fire Phone and details revealed about the Google Android Wear SDK suggest another important dimension: the competitive advantage of rapid, frictionless… Read More

Rise of the cloudphone?

We’re all quite twitterpated with the smartphone. Admittedly, it has taken much of the world by storm, and dominates EDA discussion because of the complex SoCs inside. Feature phones have repeatedly been declared dead, or at least disinteresting, but the numbers tell a different story.

While Europe and the US enjoy much higher… Read More

What does a 52% increase in DSP IP core licensing means?

The future market performance for an IP vendor licensing an IP based on a model with upfront fee plus royalties can be easily and safely evaluated if you look at the first part of revenue: upfront fee. Even if the royalty part is declining, exhibiting a 52% increase (Q4 2013 to Q4 2012) in upfront licensing fee is a promise that the future… Read More

The DSP is dead! Long Live the DSP… IP core!

Trying to trace DSP birth as a standard IC product, you come back to the early 80’s, when a certain Computer manufacturer named IBM has asked to a certain Semi-Conductor giant (at that time) named Texas Instruments if they could turn a lab concept, Digital Signal Processor, into a standard product that IBM could buy to TI, like they… Read More

4 Billion CEVA powered Chips shipped

Why making the difference between chips and cores, when mentioning that CEVA’s customers have shipped four billion IC to date? Because that can make a big difference! Imagine for example an IP vendor selling processor IP cores to be used in massively parallel computing application, when the chip maker create a processor NxM matrix,… Read More