We are excited to announce that Truechip, a leading provider of Verification IP solutions, will be actively participating at DAC 2024, taking place from June 23-25 at Moscone West, San Francisco, CA. This event is a pivotal gathering for professionals in the verification industry, and Truechip’s presence will be a highlight … Read More

Tag: dsi

Reducing Electronic Systems Design Complexity with AI

In the world of electronic systems design, complexity has always been a major challenge. As technology advances and demands for more efficient and powerful electronic devices grow, engineers face increasingly intricate design requirements. These complexities often lead to longer design cycles, increased costs, … Read More

Synopsys Webinar: MIPI Adoption Beyond Mobile, it’s now!

Some of the various MIPI specifications are now massively used in mobile (smartphone or tablet), especially the Multimedia related specs like Camera Serial Interface (CSI-2), Display Serial Interface (DSI) and D-PHY. You have to implement with CSI-2 or DSI controller a serial based physical interface, D-PHY specified up to… Read More

MIPI DevCon 2016: Opened to non-MIPI Members!

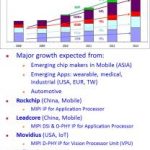

The MIPI Alliance was founded in 2003 by large IDM to standardize chip-to-chip interfaces in the wireless phone (mobile) segment. The various MIPI specifications (CSI, DSI, DigRF and many more) have been adopted by the application processor chip makers (usually large IDM or fabless, like Intel or Qualcomm initially and many … Read More

MIPI CSI-2 and DSI IP? Better with FPGA Prototyping Set

Sourcing MIPI CSI-2 or DSI IP to a respected IP vendor is mandatory to build a peripheral IC or a SoC targeting mobile application as the chip maker simply can’t afford to do a re-spin because of Time-To-Market imperative. Buying this IP to a vendor also offering MIPI powered FPGA Prototyping Platforms is even better! Northwest Logic… Read More

Semiwiki Blogger at DAC: MIPI Beyond Mobile, Myth or Reality?

Some of the various MIPI specifications are now massively used in mobile (smartphone or tablet), especially the Multimedia related specs like Camera Serial Interface (CSI-2), Display Serial Interface (DSI) or SoundWire (even if the spec has been released in December 2014, the adoption rate is very sharp, no doubt that it will… Read More

Innovative MIPI Display Solution for UHD Mobile Devices

Today an SoC cannot be without multiple IP blocks integrated together in the most optimal manner. In such an environment, it’s natural that interoperability and configurability of an IP get prime considerations to achieve the best PPA (Power, Performance and Area) for the SoC containing that IP. While PPA is a basic criterion … Read More

MIPI Alliance introduces C-PHY, Synopsys launch C-PHY VIP

The set of MIPI PHY specifications has enlarged during last night, as theMIPI Alliance has introduced the new C-PHY spec on September 17th, a physical layer interface for camera and display applications. “The MIPI C-PHY specification was developed to reduce the interface signaling rate to enable a wide range of high-performance… Read More

Getting the best from MIPI IP Toolbox

The set of MIPI specifications has severely enlarged during the past year. This is a positive point, as the large set of specifications induces a wider choice, and a chip maker can decide to implement a complex specification to differentiate with competitors, or select a specification just tailored to support a basic architecture… Read More

MIPI Alliance Specifications Adoption Status in 2013

At the beginning of December in Paris I had the opportunity to make a presentation to a very impressive audience, technical gurus from companies contributing to MIPI Alliance specification were here, including ST-Microelectronics, Intel, Qualcomm, TI, Toshiba, Nokia, Samsung, to name a few. … Read More