For SOC designers that are waiting for library models the saying “give me liberty or give me death” is especially apropos. Without libraries to support the timing flow, SOC design progress can grind to a halt. As is often the case, more than just a few PVT corners are needed. Years ago, corners were what the term sounded like – the 4 corners… Read More

Tag: daniel nenni

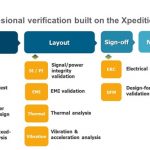

Eliminate PCB Re Spins using an Integrated Multi Dimensional Verification Platform

The rapidly increasing complexity of today’s designs, combined with schedule pressure to deliver innovative products to market as quickly as possible, strains engineering resources to the limit, often to the point of breaking. As a result, 17% of all projects get canceled, and another 28% miss their target release date (Source:… Read More

Intel Diversity Semiconductors

Growing up in a military family, mostly in California, I would consider my cultural diversity life experience to be more than most. I remember in the 1960s some older folks were chattering about a colored family moving into our neighborhood and they had a son my age. Imagine my excitement as a child in having a multicolored friend!… Read More

Honey I Shrunk the EDA TAM

The “20 Questions with Wally Rhines” series continues

Throughout the history of the EDA industry, pricing models have caused discontinuities in the way the industry operates. For a variety of competitive reasons, individual companies have developed ways to change the pricing model in an attempt to secure competitive… Read More

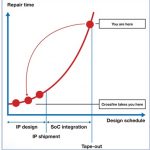

Crossfire Baseline Checks for Clean IP at TSMC OIP

IP must be properly qualified before attempting to use them in any IC design flow. One cannot wait to catch issues further down the chip design cycle. Waiting for issues to appear during design verification poses extremely high risks, including schedule slippage. For example, connection errors in transistor bulk terminals where… Read More

Turnkey 2.5D HBM2 Custom SoC SiP Solution for Deep Learning and Networking Applications

Before we jump into the specifics, let us understand what’s driving custom solutions in the high performance computing and networking space. It’s the growing demand for core capacity and greater performance, which is due to the increase in the level of parallelism and multitasking required to handle the enormous amount of data… Read More

Accelerating Design and Manufacturing at the 25th Annual IEEE Electronic Design Process Symposium

25th annual IEEE Electronic Design Process Symposium

Accelerating Design and Manufacturing

September 13 & 14, 2018, SEMI, 673 S. Milpitas Blvd, Milpitas, CA 95035

This year marks a milestone in EDPS’s history as it turns 25. The event will be held at SEMI’s new headquarter facility and will provide a forum for EDA, foundry … Read More

The Ever-Changing ASIC Business

The cell-based ASIC business that we know today was born in the early 1980s and was pioneered by companies like LSI Logic and VLSI Technology. Some of this history is covered in Chapter 2 of our book, “Fabless: The Transformation of the Semiconductor Industry”. The ASIC business truly changed the world. Prior to this revolution,… Read More

The Importance of Daughter Cards in FPGA Prototyping

FPGA Prototyping started with the advent of FPGAs in the 1980s and today it is a fast growing market segment due to increasing chip and IP complexities up against tightening windows of opportunities. Getting your design verified quickly and allowing hardware and software engineers the opportunity to develop, test, and optimize… Read More

55DAC Trip Report IP Quality

This year I signed books in the Fractal booth (compliments of Fractal) and let me tell you it was quite an experience. IP quality is a very touchy subject and the source of many more tape-out delays than I had imagined. As it turns out, commercial IP is the biggest offender which makes no sense to me whatsoever. Even more shocking, one… Read More