The foundation of SemiWiki.com has always been to transition live semiconductor related events to an easy to digest digital format via a worldwide online semiconductor community. SemiWiki is staffed by working semiconductor professionals that transform live events, press releases, whitepapers, webinars and other collateral… Read More

Tag: daniel nenni

Is the ASIC Business Dead?

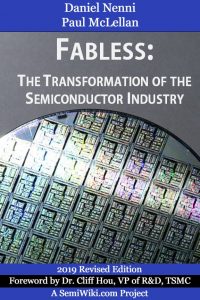

We covered the ASIC business in Chapter 2 of our book “Fabless: The Transformation of the Semiconductor Industry” using VLSI Technology and eSilicon as shining examples. Neither of which now exist. The ASIC business model was a critical steppingstone in the transformation of the semiconductor industry. Many systems companies… Read More

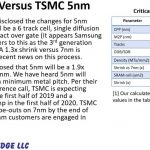

TSMC Update Q3 2019 Absolutely!

This will be a combination of the recent TSMC quarterly report, a look back at Cliff Hou’s keynote at the most recent TSMC conference, and conversations on SemiWiki.com. There has been a lot of press on this but of course the most important points are being missed. Semiconductors are complicated and getting more so, absolutely.… Read More

Webinar: VLSI Design Methodology Development (new text)

Daniel Nenni was gracious enough to encourage me to conduct a brief webinar describing a new reference text, recently published by Prentice-Hall, part of the Semiwiki Webinar Series.

VLSI DESIGN Methodology Development Webiner Replay

Background

I was motivated to write the text to provide college students with a broad background… Read More

Webinar – Fabless: The Transformation of the Semiconductor Industry 2019 Update!

As more than 343 people (and counting) know, we will be releasing the 2019 updated PDF version of our first book “Fabless: The Transformation of the Semiconductor Industry” via handout at a live webinar. The response has been overwhelming and I want to personally thank you. The webinar will be a brief overview of the book with a question… Read More

An Update from Joe Sawicki @ Mentor, a Siemens Business 56thDAC

Executives from the major EDA companies attend the Design Automation Conference to introduce new product features, describe new initiatives and collaborations, meet with customers, and participate in lively conference panel discussions. Daniel Nenni and I were fortunate to be able to meet with Joe Sawicki, Executive Vice… Read More

Ten Things to see @ 56th DAC!

New products always take precedence since EDA is a “mature” market. I have inside knowledge on this one so I can tell you it is not to be missed. Coincidently, but not really, a related white paper was just published so if you are not going to 56thDAC you can still get a virtual briefing. If you are going to DAC be sure and stop by the Fractal… Read More

Physical Design for Secure Split Manufacturing of ICs

Semiconductors are not only critical to modern life, semiconductors are critical to National Security. Now that leading edge semiconductor foundries have left the United States one of the more pressing challenges is secure semiconductor manufacturing. This applies to all countries of course so let’s take a look at the International… Read More

Semiconductor Security and Sleep Loss

One of the semiconductor topics that keeps me up at night is security. We track security related topics on SemiWiki and while the results are encouraging, we still have a very long way to go. Over the last three years we have published 148 security related blogs that have garnered a little more than 400,000 views. Security touches … Read More

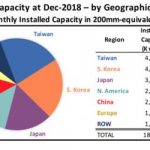

TSMC and Semiconductors 2019 and Beyond

TSMC has always been my bellwether and for 2019 I think we need to pay careful attention. Bad economic news has been spreading inside the fabless semiconductor ecosystem (tool and IP budgets have been tightening) but I think it is a bit premature. Let’s take a look at the TSMC 2018 Q4 earnings call and talk more about it in the comments… Read More