Compared to the automation of digital design, the development of automation for analog has taken a much more arduous path. Over the decades there have been many projects both academic and commercial to accelerate and improve the process for analog design. One of the most interesting efforts in this area is being spearheaded by … Read More

Tag: chiplet

Podcast EP54: Ventana Micro, RISC-V, HPC and Chiplets

Dan is joined by Balaji Baktha, founder and CEO of Ventana Micro. Balaji explores the application of RISC-V in high-performance applications and the specific advantages of a chiplet-based approach.

RISC-V Summit Panel: https://www.youtube.com/watch?v=duZaAhWxhWM

The views, thoughts, and opinions expressed in these… Read More

CEO Interview: Mo Faisal of Movellus

Prior to founding Movellus, Dr. Faisal held positions at semiconductor companies such as Intel and PMC Sierra. Faisal received his B.S. from the University of Waterloo, and his M.S. and Ph.D. from the University of Michigan, and holds several patents. Dr. Faisal was named a “Top 20 Entrepreneur” by the University of Michigan Zell… Read More

Die-to-Die Connections Crucial for SOCs built with Chiplets

If you ascribe to the notion that things move in circles, or concentrically, the move to die-to-die connectivity makes complete sense. Just as multi-chip modules (MCM) were the right technology decades ago to improve power, areas, performance and cost, the use of chiplets with die-to-die connections provides many advantages… Read More

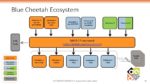

Blue Cheetah Technology Catalyzes Chiplet Ecosystem

There are many reasons today for dividing up large monolithic SoCs into chiplets that are connected together inside a single package. Let’s look at just some of these reasons. Many SoCs share a common processing core with application specific interfaces and specialized processing engines. Using chiplets would mean that it is… Read More

Alchip at TSMC OIP – Reticle Size Design and Chiplet Capabilities

This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. This presentation is from Alchip, presented by James Huang,… Read More

Optimizing Chiplet-to-Chiplet Communications

Summary

The growing significance of ultra-short reach (USR) interfaces on 2.5D packaging technology has led to a variety of electrical definitions and circuit implementations. TSMC recently presented the approach adopted by their IP development team, for a parallel-bus, clock-forwarded USR interface to optimize power/performance/area… Read More

TSMC – Solid Q3 Beat Guide- 5G Driver – Big Capex Bump – Flawless Execution

TSMC puts up solid QTR, Capex increase for 5NM and capacity increase, 5G/mobile remains driver- HPC good 7NM, 27% of revs- Very nice margins!

In line quarter-Good guide

TSMC reported revenues of $9.4B and EPS of $0.62 , more or less in line with expectations, perhaps a touch below ” whisper” expectations which had been… Read More

eSilicon White Paper on Chiplets – Good Read

eSilicon recently released a paper detailing its experiences and its thoughts on the future of chiplets. The author of the white paper is Dr. Carlos Macián. I have also covered a presentation given by Carlos recently at the AI Hardware Summit, and he is well-spoken and quite knowledgeable. To get the white paper, go to the eSilicon… Read More

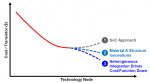

A Future Vision for 3D Heterogeneous Packaging

At the recent Open Innovation Platform® Ecosystem Forum in Santa Clara, TSMC provided an enlightening look into the future of heterogeneous packaging technology. Although the term chiplet packaging is often used to describe the integration of multiple silicon die of potentially widely-varying functionality, this article… Read More