Siemens EDA’s next move in its Calibre shift left strategy is the addition of correct-by-construction IC layout optimization for the most critical emerging physical design challenges. Calibre’s new DesignEnhancer product supports both custom and digital ICs and is already in use by several leading IC design companies. It … Read More

Tag: calibre

Podcast EP170: An Overview of the New Calibre Shift-Left Methodology with Jeff Wilson

Dan is joined by Jeff Wilson, the DFM director of product management for Calibre Design Solutions at Siemens EDA. Jeff is responsible for the development of products and design flows that address the challenges of DFM and increasing the robustness of designs.

Dan explores the capabilities of the new Calibre Design Enhancer product… Read More

Calibre IC Manufacturing papers at SPIE 2023

The Siemens Calibre group was very busy last week at SPIE. Calling Calibre industry leading really is an understatement. Calibre is one of the reasons Moore’s Law has continued to this day. This tool is legendary. You can get more information on the Calibre landing page including product information, resource guide, blogs

Building better design flows with tool Open APIs – Calibre RealTime integration shows the way forward

You don’t often hear about the inner workings of EDA tools and flows – the marketing guys much prefer telling us about all the exciting things their tools can do rather than the internal plumbing. But this matters for making design flows – and building these has largely been left to the users to sort out. That’s an increasing challenge… Read More

EDA in the Cloud with Siemens EDA at #59DAC

Tuesday at DAC I had the pleasure of attending the Design on Cloud Theatre where experts from Siemens EDA gave an update on what they’ve been offering to IC and systems designers. I remember attending a cloud presentation from Craig Johnson in 2021, so I was keen to note what had changed in the past 12 months.

Industry Trends,

… Read MoreCalibre, Google and AMD Talk about Surge Compute at #59DAC

In 2022 using the cloud for EDA tasks is a popular topic, and at DAC this year I could see a bigger presence from the cloud hardware vendors in the exhibit area, along with a growing stampede of EDA companies. Tuesday at DAC there was a luncheon with experts from Siemens EDA, Google and AMD talking about surge compute. I already knew Michael… Read More

Electromigration and IR Drop Analysis has a New Entrant

My first IR drop analysis was back in the early 1980s at Intel, where I had to manually model the parasitics of the VDD and VSS interconnect for all of the IO cells that our team was designing in a graphics chip, then I ran that netlist in a SPICE simulator using transient analysis, measuring the bounce in VSS and droop in VDD levels as all… Read More

AMS IC Designers need Full Tool Flows

Digital IC design gets a lot of attention, because all of our modern devices primarily use digital logic, but in reality whenever you have a sensor like a camera, accelerometer, gyroscope or any radio like Bluetooth, WiFi or NFC, then you’re really in the realm of analog, and that’s where mixed-signal IC design comes… Read More

EDA in the Cloud – Now More Than Ever

A decade ago, many of us heard commentaries on how entrepreneurs were turned down by venture capitalists for not including a cloud strategy in their business plan, no matter what the core business was. Humorous punchlines such as, “It’s cloudy without any clouds” and “Add some cloud to your strategy and your future will be bright… Read More

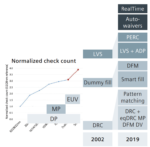

RealTime Digital DRC Can Save Time Close to Tapeout

Over the years DRC tools have done an admirable job of keeping pace with the huge growth of IC design size. Yet, DRC runs for sign off on the full design using foundry rule decks take many hours to complete. These long run times are acceptable for final sign off, but there are many situations where DRC results are needed quickly when small… Read More