Selectively automating non-critical aspects of custom IC design allows engineers to focus on precision-crafting their designs. Cadence circuit design solutions enable fast and accurate entry of design concepts, which includes managing design intent in a way that flows naturally in the schematic. Using this advanced, parasitic-aware… Read More

Tag: cadence

MemCon Returns

Back before Denali was acquired by Cadence they used to run an annual conference called MemCon. Since Denali was the Switzerland of EDA, friend of everyone and enemy of none, there would be presentations from other memory IP companies and from major EDA companies. For example, in 2010, Bruggeman, then CMO of Cadence, gave the opening… Read More

Shorter, better and easier PCIe and NVM Express Verification flow with advanced technologies

We have talked about Cadence subsystem IP strategy, illustrated by NVM Express subsystem IP, in a previous blog. What we said was that “A subsystem IP based approach will also speed up the software development and validation phase: if the IP provider is able to propose the right tools, like the associated Verification IP (VIP), … Read More

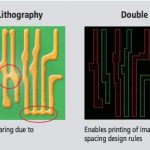

An Approach to 20nm IC Design

Last month at DAC I learned how IBM, Cadence, ARM, GLOBALFOUNDRIES and Samsung approach the challenges of SoC design, EDA design and fabrication at the 20nm node. Today I followed up by reading a white paper on 20nm IC design challenges authored by Cadence, a welcome relief to the previous marketing mantra of EDA 360.

Here’s… Read More

How has 20nm Changed the Semiconductor Ecosystem?

What does mango beer have to do with semiconductor design and manufacturing? At a table of beer drinkers from around the world I would have never thought fruity beer would pass a taste test, not even close. As it turns out, the mango beer is very good! Same goes for 20nm planar devices. “Will not work”, “Will not yield”, “Will not scale”,… Read More

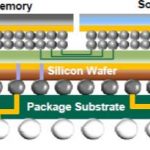

Cadence at Semicon West Next Week: 2.5D and 3D

Next week it is Semicon West in the Moscone Center from Tuesday to Thursday, July 10-12th. Cadence will be on a panel session during a session entitled The 2.5D and 3D packaging landscape for 2015 and beyond. This starts with 3 short keynotes:

- 1.10pm to 1.25pm: Dr John Xie of Altera on Interposer integration through chip on wafer on

Cadence’s NVM Express: fruit from subsystem IP based strategy

If we look at SoC design evolution, we have certainly successfully passed several steps: from transistor by transistor IC design using Calma up to design methodology based on the integration of 500K + gates IP like PCIe gen-3 Controller, one out of several dozens of IP integrated in today’ SoC for Set-Top-Box or Wireless Application… Read More

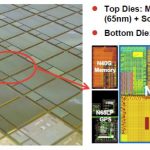

Cadence/TSMC 3D

Mark Twain remarked that everyone talks about the weather but nobody does anything about it. 3D ICs seems to be a bit like that. Over the last couple of years there have been lots of people talking about 3D but very little that has actually been manufactured. In addition to the weather, everyone talks about Xilinx’s 3D Virtex… Read More

ST using Cadence IC Tools with Module Generators

Cadence invited Francois Lemery of ST Microelectronics to speak at a luncheon last Monday at DAC about designing for the 20nm node using module generators. Here are my trip report notes:

Collaboration at 28nm, 20nm and 14nm

Wednesday morning I attended a panel discussion with: ARM, IBM, Cadence, GLOBALFOUNDRIES and Samsung.

The panelists all sang the same song of collaboration between EDA, IP and Foundry to enable 28nm, 20nm and even 14nm.… Read More