It is an indictment of our irrationality that our cars are now more health-conscious than we are. Increasingly safety-conscious readings of the ISO26262 standard now encourage that safety-critical electronics (anti-lock braking control for example) automatically self-test, not just at power-on but repeatedly as the car… Read More

Tag: cadence

Palladium Moves Power (and Temperature) Modeling to the System Level

I had a debate with Steve Carlson of Cadence earlier in the year at the EDPS conference on whether there were really any truly effective solutions for doing power estimation in emulation. I thought there weren’t and he said I was wrong. After attending the Cadence front-end summit last week, I have to admit he has a point.

First, who… Read More

Cadence Enters the RTL Power Estimation Game

At the Cadence front-end summit last week, Jay Roy presented the Cadence Joules solution for RTL (and gate-level) power estimation. Jay is ex-Apache, so knows his way around RTL power estimation which should make Joules a product to watch. Joules connects very natively to Palladium for power characterization for realistic software… Read More

Optimizing power for wearables

I was at the Cadence front-end summit this week; good conference with lots of interesting information. I’ll start with a panel on optimizing power for wearables. Panelists were Anthony Hill from TI, Fred Jen from Qualcomm, Leah Clark from Broadcom and Jay Roy from Cadence. Panels are generally most entertaining when the panelists… Read More

Globalfoundries 22FDX Technology Shows Advantages in PPA over 28nm Node

I really enjoy ARM Techcon when it rolls around every year because it has such a wide range of topics and exhibits. You can find maker gadgets, IoT information, small boards for industrial control, software development kits, semiconductor IP vendors as well as the big EDA players and foundries. This year after perusing the exhibit… Read More

Maybe Clockless Chip Design’s Time has Come

There have always been novel technologies vying to compete with conventional design practices. It is hit or miss on the success of these ideas. In the 90’s I recall speaking to someone who was convinced that they could effectively build computers based on multilevel logic. This, as we know did not pan out. But there have been many … Read More

A (R)evolution in Hardware-based Simulation Acceleration

The most exciting products in our industry are those that are both evolutionary and revolutionary. Cadence has just announced an update to their hardware simulation acceleration platform – Palladium Z1 – which continues the evolution of the unique capabilities of processor-based acceleration, plus a revolutionary approach… Read More

28nm FD-SOI: A Unique Sweet Spot Poised to Grow

I have been silently watching STMicroelectronics pursuing FD-SOI technology since quite a few years. FinFET was anyway getting more attention in the semiconductor industry because of several factors involved. But from a technology as well as economic perspective there are many plus points with FD-SOI. I remember my debate,… Read More

Is This a Dagger Which I See Before Me?

Macbeth may have been uncertain of what he saw but, until recently, image recognition systems would have fared even less well. The energy and innovation put into increasingly complex algorithms always seemed to fall short of what any animal (including us humans) is able to do without effort. Machine vision algorithms have especially… Read More

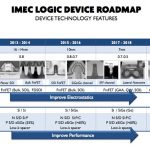

IMEC and Cadence Disclose 5nm Test Chip

Recently imec and Cadence disclosed that they had fabricated 5nm test chips. This afternoon Dan Nenni and I had a conference call with Praveen Raghavan, principal engineer at imec, and Vassilios Gerousis, distinguished engineer at Cadence to get more details on what the test chip is and what was learned.

First off Vassilios really… Read More