Check this webinar out – Mediatek will share a novel approach to early IR drop estimation. Competition in system design has become even more intense because potential markets are huge and there are more players with deep pockets chasing those markets. Wherever you are in those value chains, you want to shift everything left to accelerate… Read More

Tag: bernard murphy

Easing Your Way into Portable Stimulus

The Portable Stimulus Standard (PSS) was officially released at DAC this year. While it will no doubt continue to evolve, for those who were waiting on the sidelines, it is officially safe to start testing the water. In fact it’s probably been pretty safe for a while; vendors have had solutions out for some time and each is happy to … Read More

A Fresh Idea in Differential Energy Analysis

When I posted earlier on Qualcomm presenting with ANSYS on differential energy analysis, I assumed this was just the usual story on RTL power estimation being more accurate for relative estimation between different implementations. I sold them short. This turned out to be a much more interesting methodology for optimizing total… Read More

The Robots are Coming!

Moshe Sheier, VP Marketing at CEVA, recently got back from MWC Shanghai and commented that robots are clearly trending. He saw hordes of robots from dozens of companies, begging for someone to brand and offer them in any one of many possible applications: in an airport to guide you to a connecting flight, for elder care, in hospitals… Read More

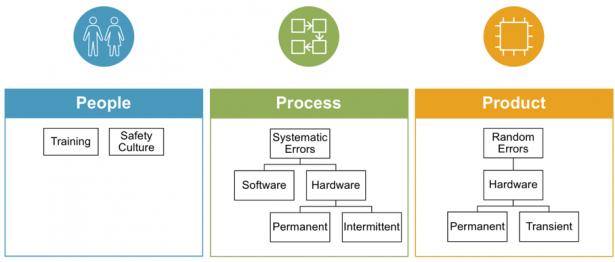

ISO 26262: People, Process and Product

Kurt Shuler, VP Marketing at Arteris IP, is pretty passionate that people working in the automotive supply chain should understand not just a minimalist reading of ISO 26262 as it applies to them but rather the broader intent, particularly as it is likely to affect others higher in the supply chain. As an active ISO 26262 working … Read More

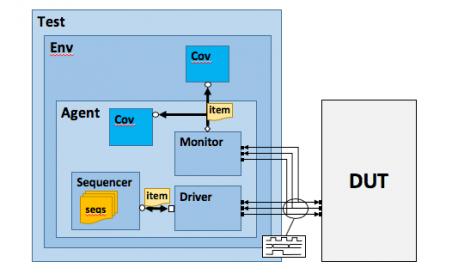

WEBINAR: A UVM Cookbook Update

Something I always admire about Mentor is their willingness to invest their time and money in helping the industry at large. They do this especially in verification where they sponsor periodic Wilson surveys on the state of verification needs and usage in the industry. More recently they introduced their UVM Cookbook, an introduction… Read More

Webinar: Ensuring System-level Security based on a Hardware Root of Trust

A root of trust, particularly a hardware root of trust, has become a central principle in well-architected design for security. The idea is that higher layers in the stack, from drivers and OS up to applications and the network, must trust lower layers. What does it help it to build great security into a layer if it can be undermined… Read More

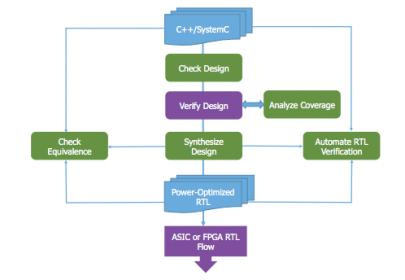

Computer Vision Design with HLS

I’m on a mini-roll on the subject of high-level design for ML-based systems. No complaints from me, this is one of my favorite domains and is certainly a hot area; it’s great to that EDA vendors are so active in advancing ML-based design. Here I want to talk about the Catapult HLS flow for use in ML design.

Since I’ve covered the ML topic… Read More

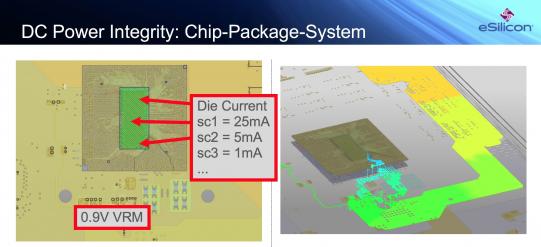

Chip, Package, System Analysis – A User View

While I missed ANSYS (and indeed everyone else) at DAC this year, I was able to attend the ANSYS Innovation Conference last week at the Santa Clara Convention Center. My primary purpose for being there was to listen to a talk by eSilicon which I’ll get to shortly, but before that I sat through a very interesting presentation on the growing… Read More

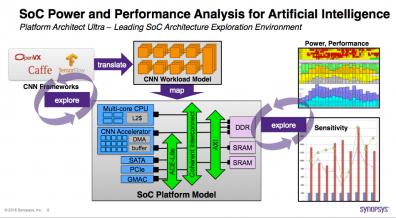

Architecting an ML Design

Discussion on machine learning (ML) and hardware design has been picking up significantly in two fascinating areas: how ML can advance hardware design methods and how hardware design methods can advance building ML systems. Here I’ll talk about the latter, particularly about architecting ML-enabled SoCs. This approach is … Read More