You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

If you’re new to PSS you could be forgiven for thinking that it automagically makes stimulus reusable, vertically from IPs to systems, horizontally between derivatives and between hardware-based and software-based testing. From a big-picture point of view these are certainly all potential benefits of PSS.

What PSS does provide… Read More

OK, so you’re in a giant mall, you want to find a store that sells gloves and you want to know how to get there. Or you’re in a supermarket and you need some obscure item, say capers, that doesn’t really fall under any of the main headings they post over the aisles. If you’re like most of us, certainly like me, this can be a frustrating experience.… Read More

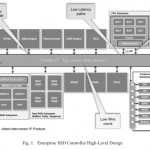

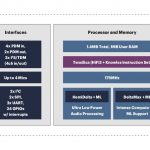

The use of safety-centric logic design techniques for automotive applications is now widely appreciated, but did you know that similar methods are gaining traction in the design of enterprise-level SSD controllers? In the never-ending optimization of datacenters, a lot attention is being paid to smart storage, offloading… Read More

A lot of the attention in intelligent systems is on object detection in still or video images but there’s another very active area, in smart audio. Amazon and Google smart speakers may be the best-known applications but there are more obvious (and perhaps less novelty-driven) applications in enhancing the hearing devices we already… Read More

In the semiconductor world when we hear “full-stack” we think of a chip, chipset or board with a bunch of software, which can be connected to sensors of various types on one end, trained networks in the middle and actuators on the other side. But of course that’s not really a full-stack. The real thing would be deployment of an entire… Read More

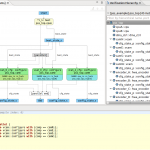

Portable stimulus has been a hot topic for a couple of years in the EDA and semiconductor industries. Many observers see this approach as the next major advance in verification beyond the Universal Verification Methodology (UVM), and the next step higher in abstraction for specifying verification intent. The basic idea is to … Read More

AI accelerators as engines for object or speech recognition (among many possibilities), are becoming increasingly popular for inference in mobile and power-constrained applications. Today much of this inferencing runs largely in software on CPUs or GPUs thanks to the sheer size of the smartphone market, but that will shift… Read More

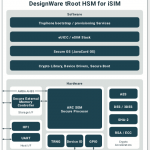

I’m a believer that connectivity for the IoT at scale (the trillions of devices that the industry predicts) has to be cellular. This is partly based on reach, particularly outside urban areas, but is mostly based on the financial implications of that scale. Yes, you can build infrastructure for say local Wi-Fi support with backhaul… Read More

If you practice in advanced levels of power management, you know about dynamic voltage and frequency scaling (DVFS). This is where you allow some part of a circuit, say a CPU, to run at different voltages and frequencies depending on acceptable performance versus thermal tradeoffs and battery life on a mobile device. Need to run… Read More

Arm is a machine. They crank out new products in a wide range of categories, Project Trillium for AI, Neoverse for infrastructure, their Automotive Enhanced line and the Pelion IoT platform. And in each they have a regular beat of new product introductions following roadmaps they have already laid out. Not that you’d expect any … Read More