I am talking about the health of electronic and semiconductor design, which if made sound at RTL stage, can set it right for the rest of the design cycle for faster closure and also at lesser cost. Last week was the week of ITC(International Test Conference) for the Semiconductor and EDA community. I was looking forward to what ITC… Read More

Tag: atrenta

SpyGlass: Focusing on Test

For decades we have used a model of faults in chips that assumes that a given signal is stuck-at-0 or stuck-at-1. And when I say decades, I mean it. The D-algorithm was invented at IBM in 1966, the year after Gordon Moore made a now very famous observation about the number of transistors on an integrated circuit. We know that stuck-at… Read More

Innovation + Thoughtful Management = Productive Expansion

After looking at various aspects of this company, to sum up, I couldn’t find any better statement than this; thoughtful management here is actually leadership with passion which achieves tangible results. This reflects in the methodology of doing things in this company which has given it a place among top EDA companies in a span… Read More

Atrenta Seminars in Asia – Making RTL Signoff Real

Engaging with the semiconductor ecosystem is critical to surviving in the fast paced times we work in. Face to face interaction at all levels is key and semiconductor IP is a prime example. How do you ensure that your IP meets objective quality requirements before integration into your SoC, and that your SoC is ready for handoff to… Read More

Electronic System Level: Gary Smith

Gary Smith has been talking about how the electronic system level (ESL) is where the future of EDA lies as design teams move up to higher levels encompassing IP blocks, high level synthesis, software development using virtual platforms and so on. At DAC this year in Austin he talked about how the fact that EDA controls the modeling… Read More

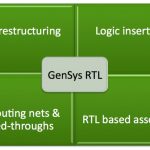

From Layout Sign-off to RTL Sign-off

This week, I had a nice opportunity meeting Charu Puri, Corporate Marketing and Sushil Gupta, V.P. & Managing Director at Atrenta, Noida. Well, I know Sushil since 1990s; in fact, he was my manager at one point of time during my job earlier than Cadence. He leads this large R&D development centre, consisting about 200 people… Read More

Around the World in 80 Engineers…Actually Well Over 200

Atrenta today announced Dr Ajith Pasqual, who is the Head of the Department of Electronic & Telecommunication Engineering at the University of Moratuwa in Sri Lanka (which used to be known as Ceylon) has joined Atrenta’s technical advisory board (TAB). OK, academics join EDA company’s TABs all the time so that’s… Read More

New Book on Design Constraints

There is a new book out from Springer. The subtitle is actually a better description that the title. The subtitle is A Practical Guide to Synopsys Design Constraints (SDC) but the title isConstraining Designs for Synthesis and Timing Analysis. The authors are Sridhar Gangadharan of Atrenta in San Jose and Sanjay Churiwala of Xilinx… Read More

When Atrenta celebrates with STM and CEA-Leti in Grenoble

Grenoble is French city well-known within the Semiconductor industry to be one of the last location counting wafer fabs, not only in France but in fact in Europe. Back in the 70’s, under French government impulse, through the Commisariat à l’Energie Atomique (CEA) and the LETI subsidiary in charge of Electronic related research,… Read More

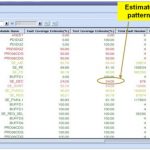

Derivative Designs Need Tools Too

Increasingly, SoC designs consist of assembling blocks of pre-designed IP. One special case is the derivative design where not just the IP blocks get re-used but a lot of the assembly itself. For example, in the design below some blocks are added, some blocks are updated, some hierarchy is changed. But the bulk of the design remains… Read More