Ever since I can remember, and I’ve been in EDA since the early 80’s, new process development has largely focused on the latest nodes. Trailing nodes were quickly put into support mode. New nodes benefited the most from static and dynamic voltage reduction efforts, as well as improvements in flows and performance. Only a small number… Read More

Tag: arm

A Key Aspect Missing for IoT to become NBT

The IoT (Internet of Things) is not one product, technology, segment, or market. It’s a combination of many things, many markets, and many technologies. However, it’s one thing that needs to connect everything together; edge device to gateway to cloud. That brings the complexity, how’s that possible amid large heaps of heterogeneous… Read More

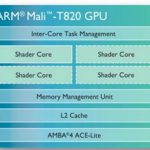

How ARM Implemented a Mali GPU using Logic Synthesis and Place/Route Tools

ARM is a well-known semiconductor IP provider and they often create a reference design so that SoC companies can have a starting point to work with. On the GPU side of IP the ARM engineers have an architecture called Mali, and a recent webinar hosted by Synopsys reviewed how the physical design area was minimized by using a combination… Read More

SEMICON Day 1: IoT Everywhere…and China

The first day of SEMICON West for me is usually imec day. They have a full day of presentations. But I saw the most interesting ones in Brussels recently so I decided to go to the SEMI/Gartner day instead. They run in parallel ballrooms in the Marriot on 4th street.

To me there were two big themes. One was the unavoidable internet of things… Read More

Angela Merkel Visits GlobalFoundries in Dresden!

The Chancellor of Germany visited Fab 1 in Dresden today. I did not get to speak with her personally so I will send her a message here. The fabless semiconductor industry is a force of nature. You can either harness the power or be overwhelmed by it. The United States, Taiwan, China, and South Korea have certainly figured this out. Hopefully… Read More

Power Management Gets Tricky in IP Driven World

Today, an SoC can have multiple instances of an IP and also instances of many different IPs from different vendors. Every instance of an IP can work in a separate mode and requires a dedicated power arrangement which may only be formalized at the implementation stage. The power intent, if specified earlier, will need to be re-generated… Read More

Xilinx Datacenter on a Chip

I talked recently about the Intel acquisition of Altera which seems to be all about using FPGA technology to build custom accelerators for the datacenter. Some algorithms, especially in search, vision, video and so on map much better onto a hardware fabric than being implemented in code on a regular microprocessor.

So if the heart… Read More

SmartDV at DAC and More

As we are aware about SmartDV Technologies, a fast emerging company in IP space with offices in Bangalore and San Diego, its booth in 52ndDACwas located at a prominent position in front of DAC Pavilion on the exhibits floor. So, most of the crowd coming to attend sessions in DAC Pavilion had a glimpse of SmartDV. I met Deepak Kumar Tala… Read More

eSilicon ♥ ARM!

The things I enjoy the most at conferences are presentations by customers, the companies that solve the problems we face every day with modern semiconductor design. We all have access to the same tools and IP and use the same foundries so it’s the actual design and implementation that separates the wheat from the chaff, absolutely.… Read More

Why Did Intel Pay $15B For Altera?

While I was at the imec Technology Forum someone asked me “Why did Intel pay $15B for Altera?” (the actual reported number is $16.7B).

The received wisdom is that Intel decided that it needs FPGA technology to remain competitive in the datacenter. There is a belief among some people that without FPGA acceleration available for vision… Read More