Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

Tag: apache

Low-Power Design Analysis and Optimization for Mobile and High-Performance Computing Applications

For several decades now consumers like me have enjoyed using mobile devices including:

- Transistor radios, my first one had just 6 discreet transistors in the 1960’s

- HP 21 Calculator, used in college with Reverse Polish Notation, circa 1976

- Zenith Data Systems laptop, with two floppy drives, 1980’s

- Palm Pilot V,

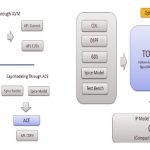

An EDA Acquisition that Worked

I first heard about Andrew Yang back in 1993 when he founded a Fast SPICE company called Anagram, then acquired by Avant! in 1996. Andrew’s latest EDA company Apache Design, Inc.was started in 2001, then acquired by ANSYS in 2011. Most EDA mergers simply don’t work because of one or more reasons, like:

- Incompatible

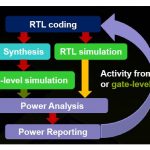

RTL Design For Power

My Samsung Galaxy Note II lasts about two days on a single battery charge, which is quite the improvement from the Galaxy Note I with only a one day battery charge. Mobile SoCs are being constrained by battery life limitations, and consumers love longer-laster devices.

There are at least two approaches to Design For Power:

- Gate-level

Power and Reliability Sign-off – A must, but how?

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

Efficient Power Analysis and Reduction at RTL Level

It’s a classic and creative example of design and EDA tool community getting together, exploiting tool capabilities and developing flows which add value to all stake holders including the end consumer. We know power has become extremely important for battery life in smart phones, high performance servers, workstations, notebooks… Read More

Full Chip IR Drop Analysis using Distributed Multi Processing

IR drop analysis across your board, package and SoC ensures that your Power Delivery Network (PDN) is robust, and that your system will function to spec. There are both static and dynamic approaches to IR drop analysis of a full-chip with billions of transistors, while the dynamic approach produces the most accurate results compared… Read More

Today’s Program is Brought To You by the Letter A

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

SemiWiki Top 10 Must See @ #50DAC List!

This list was compiled by the SemiWiki bloggers highlighting emerging technologies that we have written about and that will be demonstrated at the Design Automation Conference next week. We highly recommend you investigate them further during your time in Austin and please let us know what you think.

Today SemiWiki has more than… Read More

Samsung’s Life of Pi @ Apache @ DAC

Last week I talked to Eileen You of Samsung-SSI to get a preview on what they will be talking about at Apache’s customer theater at DAC. Their presentation is titledThe Life of PI: SoC Power Integrity from Early Estimation to Design Sign-off. The ‘PI’ stands for Power Integrity.

Samsung-SSI’s operations… Read More