The way we are seeing technology progression these days is unprecedented. It’s just about six months ago, I had written about the intense collaboration between ANSYSand TSMCon the 16nm FinFET based design flow and TSMC certifying ANSYS tools for TSMC 16nm FF+ technology and also conferring ANSYS with “Partner of the Year” award.… Read More

Tag: ansys

ANSYS Event to Highlight Cutting Edge Technology Development

If you follow technology news, it would be hard to deny that we live in exciting times. In some ways there is an unparalleled amount of big and cool technology development going on right now. We all have followed the rise of Tesla Motors. They took over a long vacant US big-auto plant in Fremont and are reinventing the US automobile industry.… Read More

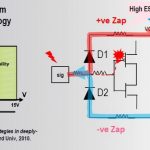

SoCs More Vulnerable to ESD at Lower Nodes

Electro Static Discharge (ESD) has been a major cause of failures in electronic devices. As the electronic devices have moved towards high density SoCs accommodating ever increasing number of gates at lower process nodes, their vulnerability to ESD effects has only increased. Among the reasons for ESD failures in SoCs, device… Read More

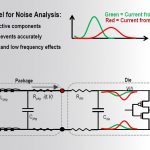

On-Chip Power Integrity Analysis Moves to the Package

Power regimes for contemporary SOC’s now include a large number of voltage domains. Rail voltages are matched closely to the performance and power requirements of various portions of the design. Indeed, some of the supply voltages are so low that the noise margins in these domains is exceedingly low. Higher voltage domains are… Read More

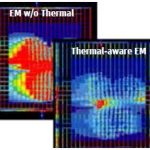

FinFET Designs Need Early Reliability Analysis

In a world with mobile and IoT devices driven by ultra-low power, high performance and small footprint transistors, FinFET based designs are ideal. FinFETs provide high current drive, low leakage and high device density. However, a FinFET transistor is more exposed to thermal issues, electro migration (EM), and electrostatic… Read More

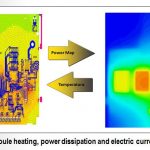

ANSYS Talks About Multi Physics for Thermal Analysis at DesignCon

ANSYS makes a big deal of being a multi-physics company. Still it has taken them a while to fully integrate Apache. Nevertheless it seems like there is a compelling argument for combining technologies to solve SOC design problems. Frankly most chip designers would be hard pressed to think of a reason for using computational fluid… Read More

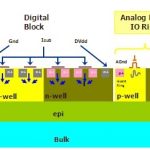

Analyze Substrate Noise in SoC Design?

Often substrate noise analysis takes place when everything is there on the chip, but that stage comes near the tape-out which is too late to make major changes in architecture, placement, introducing noise protection circuitry for the victims and so on. It was okay when there used to be very little analog content on the chip. But … Read More

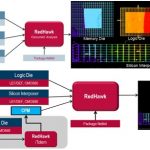

Solution for PI, TI & SI Issues in 3D-ICs

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

Noise & Reliability of FinFET Designs – Success Stories!

I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More

ANSYS Electronics Simulation Expo – A View from Industry

As we are seeing more and more automation in most of our activities, not only through software but also smart electronics (at cutting-edge technologies) equipped with processors, micro-controllers, sensors and so on which make a whole system as an integrated entity on a small piece of semiconductor intertwined with other systems… Read More