Cliff Hou of TSMC gave the keynote today at SNUG on Collaborate to Innovate: a Foundry’s Perspective. Starting around 45nm the way that a foundry has to work with its ecosystem fundamentally changed. Up until then, each process generation was similar enough to the previous one, apart obviously from size, that it could be … Read More

Tag: 28nm

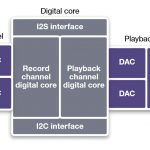

Shrinking audio creates issues and opportunities

There is a lot more to sound than meets the ear, and there a vast number of ways to deliver an audio experience. I recently trashed my gaming headset, replacing it with a Samson C03U mic and Audio-Technica ATH-PRO700MK2 headphones. It’s a huge upgrade, especially for podcasting, and I admit I was also motivated by research into digital… Read More

Winner, Winner, Chicken Dinner!

I have no idea if chicken was actually on the menu, but on December 12, Calibre RealTime picked up its thirdindustry award, this time the 2012 Elektra Award for Design Tools and Development Software from the European Electronics Industry. Calibre RealTime came out on top in a group full of prestigious finalists, including ByteSnap,… Read More

Cortex-A9 speed limits and PPA optimization

We know by now that clock speeds aren’t everything when it comes to measuring the goodness of a processor. Performance has direct ties to pipeline and interconnect details, power factors into considerations of usability, and the unspoken terms of yield drive cost.

My curiosity kicked in when I looked at the recent press release… Read More

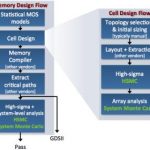

Solido and TSMC for 6-Sigma Memory Design

Solido Design Automation and TSMC recently published an article in EE Times describing how Solido’s High-Sigma Monte Carlo tool is used with TSMC PDK’s to achieve high-yield, high-performance memory design. This project has been a big part of my life for the past three years and it is time for a victory lap!

In TSMC 28nm, 20nm and … Read More

The GLOBALFOUNDRIES Files

There’s a new blogger in town, Kelvin Low from GLOBALFOUNDRIES. Kelvin was a process engineer for Chartered Semiconductor before moving on to product marketing for GF. His latest post talks about the GF 28nm SLP which is worth a read. There was quite the controversy over this Gate-First HKMG implementation of 28nm that IBM/GF/Samsung… Read More

Cadence at 20nm

Cadence has a new white paper out about the changes in IC design that are coming at 20nm. One thing is very clear: 20nm is not simply “more of the same”. All design, from basic standard cells up to huge SoCs has several new challenges to go along with all the old ones that we had at 45nm and 28nm.

I should emphasize that the paper… Read More

Qualcomm’s Moment to Re-Align Globally

Qualcomm has a nice problem to have: too much demand for its Snapdragon and 4G LTE baseband parts. How Qualcomm realigns its manufacturing strategy around this problem will determine whether or not they can breakaway from the ARM camp and go toe to toe with Intel. Last week Malcolm Penn claimed TSMC was too big to fail. Really? The … Read More

How has 20nm Changed the Semiconductor Ecosystem?

What does mango beer have to do with semiconductor design and manufacturing? At a table of beer drinkers from around the world I would have never thought fruity beer would pass a taste test, not even close. As it turns out, the mango beer is very good! Same goes for 20nm planar devices. “Will not work”, “Will not yield”, “Will not scale”,… Read More

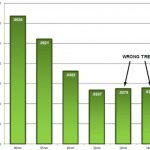

The Scariest Graph I’ve Seen Recently

Everyone knows Moore’s Law: the number of transistors on a chip doubles every couple of years. We can take the process roadmap for Intel, TSMC or GF and pretty much see what the densities we will get will be when 20/22nm, 14nm and 10nm arrive. Yes the numbers are on track.

But I have always pointed out that this is not what drives… Read More