We know the science fiction plot device from its numerous uses: in order to survive a journey of bazillions of miles across galaxies into the unknown future, astronauts are placed into cryogenic stasis. Literally frozen in time, the idea is they exit a lengthy suspension without aging, ready to go to work immediately on revival … Read More

Tag: 14nm

Handel Jones Predicts Process Roadmap Slips

At the SEMI ISS conference earlier this week, the last speaker in the technology challenges section was Handel Jones of IBS. I’ve known Handel since the mid-1980s when he came to VLSI Technology and told us we were losing money on 90% of the designs we were doing but our cost model was not good enough and so we didn’t even… Read More

New Frontiers in Scan Diagnosis

As we move down into more and more advanced process nodes, the rules of how we test designs are having to change. One big challenge is the requirement to zoom in and fix problems by doing root cause analysis on test data alone, along with the rest of the design data such as detailed layout, optical proximity correction and so on. But without… Read More

The Rosetta Stone of Lithography

At major EDA events, CEDA (the IEEE council on EDA, I guess you already know what that bit stands for) hosts a lunch and presentation for attendees and others. This week was ICCAD and the speaker was Lars Liebmann of IBM on The Escalating Design Impact of Resolution-Challenged Lithography. Lars decided to give us a whirlwind tour … Read More

ARM in Samsung 14nm FinFET

I am at ARM TechCon today. One interesting presentation was made jointly between Samsung, Cadence and ARM themselves about developing physical libraries (ARM), a tool flow (Cadence) and test chips (Samsung). It was titled Samsung ARM and Cadence collaborate on the silicon-proven world first 14-nm FinFET Cortex-A7 ARM CPU and… Read More

Yes, Intel 14nm Really is Delayed…And They Lost $600M on Mobile

Intel server profits are growing, which isn’t a big suprise. But mobile losses are high. Although the amount lost by the Other Intel Architecture Group had a loss of $606M, that is actually down slightly from Q2 but up a lot from last year when they lost “only” $235M. This group includes Atom, the Infineon Wireless… Read More

Intel 14nm versus Samsung 14nm

The legend of Intel being two process nodes ahead of the rest of the industry is quickly coming to an end. To come to terms with this you need to do an apple to apple comparison which is what I will do right here, right now.

First and foremost let’s compare SoC silicon delivery since SoCs are driving the semiconductor industry and will … Read More

Samsung 28nm Beats Intel 22nm!

There was some serious backlash to the “Intel Bay Trail Fail” blog I posted last week, mostly personal attacks by the spoon fed Intel faithful, but there are however some very interesting points made amongst the 30+ comments so be sure and read them when you have a chance.

The Business insider article “The iPhone… Read More

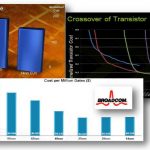

Are 28nm Transistors the Cheapest…Forever?

It is beginning to look as if 28nm transistors, which are the cheapest per million gates compared to any earlier process such as 45nm, may also be the cheapest per million gates compared to any later process such as 20nm.

What we know so far: FinFET seems to be difficult technology because of the 3D structure and so the novel manufacturing… Read More

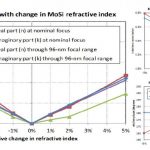

It’s a 14nm photomask, what could possibly go wrong?

Let’s start with the bottom line: in 14nm processes, errors which have typically been little more than noise with respect to photomask critical dimension (CD) control targets at larger process nodes are about to become very significant, even out of control if not accounted for.… Read More