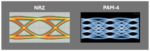

Data communication speeds continue to grow. New encoding schemes, such as PAM-4 are helping achieve faster throughput. Compared to the traditional NRZ scheme, PAM4 can send twice the signal by using four levels vs. the two used in NRZ. The diagram at the top of this post shows the how data density is increased. With progress comes… Read More

Tag: 112G serdes

Clocking for High-Speed SerDes

The incessant demand for faster data rates across a wide range of end applications has led to the development of the most recent generation of SerDes hardware, achieving 112Gbps. For example, network switches in datacenter architectures are starting to provide 51T throughput utilizing these new 112Gbps implementations (51.2Tbps… Read More

When Implementing 112G PAM4 Channels, Getting There is Half the Fun

The slogan in the title of this post originated with the cruise ship industry in the 1950s. The comment resonated then, and it continues to do so now. In a different context of course. Consider the substantial pressure for higher bandwidth channels. 5G has lit the fuse on a massive increase in wireless data volumes. IoT, autonomous… Read More

Achieving 112Gbps PAM4 Channels with Achronix FPGAs and Samtec Interconnect

They say that getting there is half the fun. On December 1, Achronix and Samtec will present a webinar on this topic in the context of high-performance front panel to midplane and midplane to backplane channel design. Technology, materials and system design will all be discussed with a focus on achieving 112Gbps PAM4 channels with… Read More

112G/56G SerDes – Select the Right PAM4 SerDes for Your Application

This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. Not all SerDes are the same. The presentation covered here,… Read More

Synopsys Webinar: A Comprehensive Overview of High-Speed Data Center Communications

High-speed communication is a critical component for many applications, most notably in the data center. The serializer/deserializer physical interface, or SerDes PHY is the backbone of many different forms of high-speed communication for this application. Use cases include on chip, between chips, between boards and racks… Read More

Monday DAC IP Session “PAM 4 Enable 112G SerDes”

This session will open the DAC IP Track at 10:30 on Monday “How PAM4 and DSP Enable 112G SerDes Design” in Room N264. I am very proud to chair this invited paper session, as it addresses one of the key pieces of design, enabling to exchange data flow at the highest possible data rate. It can be between two chips on the same board, we talk … Read More

400G Ethernet test chip tapes-out at 7nm from eSilicon

Since the beginning of May eSilicon has announced the tape-out of three TSMC 7nm test chips. The first of these, a 7nm 400G Ethernet Gearbox/Retimer design, caught my eye and I followed up with Hugh Durdan, their vice president of strategy and products, to learn more about it. Rather than just respin their 56G SerDes, they decided… Read More