I’ve spent most of my career in the ASIC business. In 2003, Gartner predicted the ASIC market would grow to $16.9B. During that time, there were a number of startups building ASICs, but the applications were a bit specialized and aimed at new markets. Consequently, there was a lot of risk to build a chip startup and many ASICs either never made it to tapeout or a perfectly good chip never found the market it was looking for. The massive cloud buildout, seemingly infinite hunger for bandwidth and the AI revolution has changed all that. Semiconductors, ASICs and even EDA are now topics that have found mainstream interest. Even the US Government seemed to have noticed. It actually feels fulfilling at some level that the rather obscure career in ASICs and EDA that I’ve pursued for my entire adult life is now of mainstream interest. A recent upbeat press release from Alchip made me smile. Alchip is painting a bright future for the ASIC market, and this kind of news feels great.

Alchip is a global provider of silicon design and production services in mainstream and advanced processes, including 7nm. The company is traded on the Taiwan and Luxembourg stock exchanges. It is headquartered in Taipei, with operations in Europe, North America, Japan, Korea, and China. Alchip is the real deal when it comes to a focused, dedicated ASIC supplier. You can find out more about Alchip on their SemiWiki page. The press release details comments recently made by James Huang, vice president, Alchip Technologies to industry executives. Mr. Huang has worked at Alchip for over 18 years, so he certainly knows something about the ASIC business.

In a presentation to industry executives, Mr. Huang pegged 2026 ASIC sales at $20 billion, up from what most analysts are pegging as a $10 billion market this year and reflecting the high-end of an anticipated 12% to 15% compound annual growth rate (CAGR). He went on to say that devices headed into networking applications will account for 45% of this year’s total market, while storage applications account for 35% and compute acceleration applications will account for the remaining 20 % of total, or $10 billion total available market (TAM). Mr. Huang estimated that North America represents the largest geographic market, while the pan-Asian region could experience the largest growth.

Mr. Huang went on to discuss the technologies that will drive this growth. Advances in heterogeneous packaging technology will be a critical piece. He explained that current 2.5D and emerging 3D packaging technology that bundles multiple “chiplets” that perform different functions would lead the charge. Mr. Huang reported that, according to Mordor Intelligence, 2.5D/3D ASICs will grow at a 35.3% CAGR between 2020 and 2025. This is spectacular growth. I am observing many of the same trends as Mr. Huang. In my view, the slowing of Moore’s Law has driven a new technology revolution around hyper-convergent design – the combination of multiple chips/chiplets and multiple technologies in a highly complex and sophisticated package.

Mr Huang predicted: “The ‘next-gen’ device that will lead industry growth will little resemble the current market leaders. They’ll be built on advanced processing technologies, at or below 3nm. Rather than a single IC, they will be integrated multi-chiplet devices in advanced 2.5D/3D CoWoS or InFO packages. They’ll will be high-power and high-frequency running at more than 400 Watts.”

Mr. Huang also provided a cautionary statement. The exponential leap in market size and functionality will require design capabilities significantly more robust than what is required today. Devices with billions of gates will require design resource investments that will represent an increase of three-to-four times, depending on complexity. As a long-time fan and participant in the EDA industry this made me smile.

Johnny Shen, president and CEO of Alchip also weighed in. “The ASIC company of tomorrow will be a very advanced technology organization. It will require a robust design methodology, flexible business model, best-in-class IP portfolio and advanced packaging technology expertise. This, as a matter of fact is the model upon which Alchip is being built today.” Having spent about half my career in the ASIC business, I couldn’t agree more with Mr. Shen. The ASIC business is NOT for wimps.

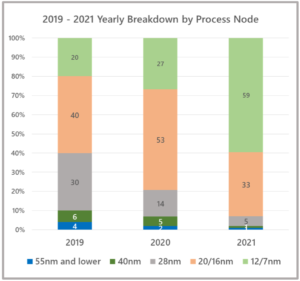

To complete the picture, Alchip recently reported that advanced technology 12/7nm designs accounted for nearly 60% of the company’s first quarter revenue. They also showed a significant growth in these types of designs over the past three years. So, there’s on ASIC supplier’s view of the future. Alchip is painting a bright future for the ASIC market, and I believe this will be an inspiration to others.

Also Read:

Maximizing ASIC Performance through Post-GDSII Backend Services

Alchip at TSMC OIP – Reticle Size Design and Chiplet Capabilities

Alchip moves from TSMC 7nm to 5nm!

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.