One of the most enduring threads in the SemiWiki forum is What would you do if you are the Intel CEO? There are currently 128 responses and more than 45,000 views. It was originally posted March 13th, 2015, after Brain Krzanich was given the CEO position. A different time for sure but an interesting read and the responses keep on coming.

One thing that struck me while watching the keynotes at IEDM is that Intel made a big change in the last few years in regard to transparency. I remember back when Intel 14nm brought FinFETs to market, we were all pleasantly surprised. Intel kept that secret like many other technology leaps that made Intel a semiconductor legend. It took the rest of the industry years to catch up and even today Intel 14nm is one of the best 14nm implementations the industry has to offer.

After the IEDM presentations by Intel and TSMC, the transparency differences were quite obvious. TSMC releases just enough information and Intel releases much more. While we all scream for transparency, in this ultra-competitive market it may not be a great idea.

The latest example is Back Side Power Delivery (BSPD). Intel first announced it at the 2022 IEEE VLSI Symposium in great detail. PowerVia was highlighted as a critical innovation to complement Intel’s gate-all-around transistor architecture (RibbonFET) and will be used first for internal products then offered to foundry customers. Here is the paper summary:

[T6-1] Intel PowerVia Technology: Backside Power Delivery for High Density and High-Performance Computing.

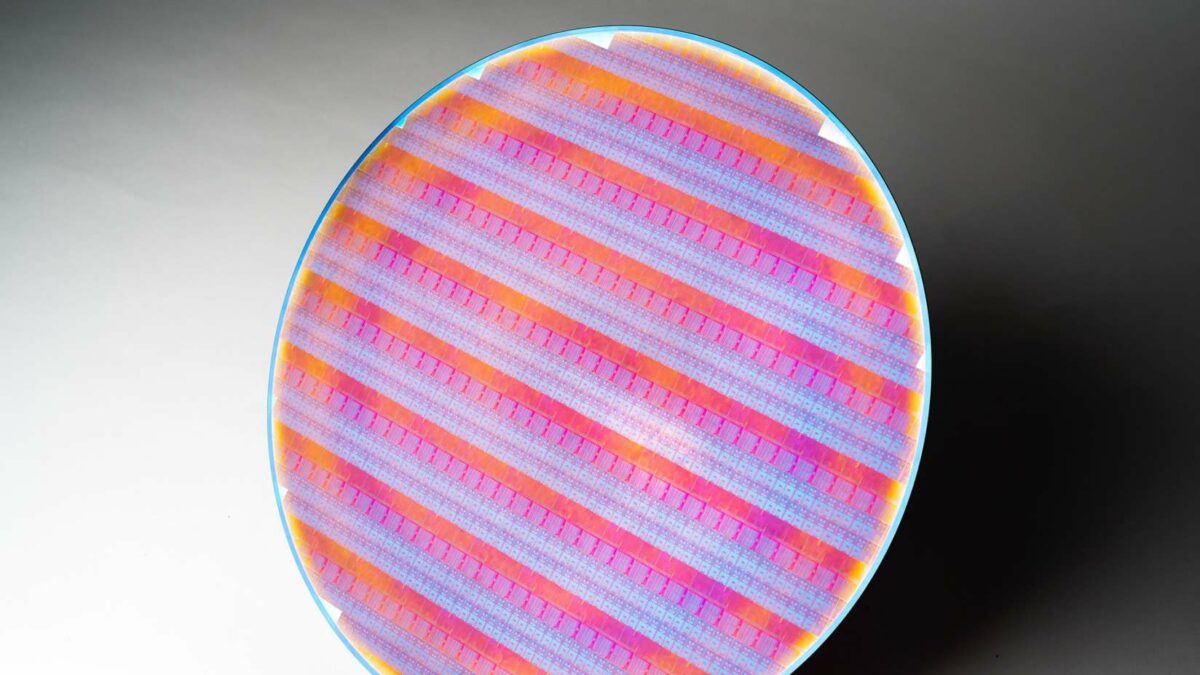

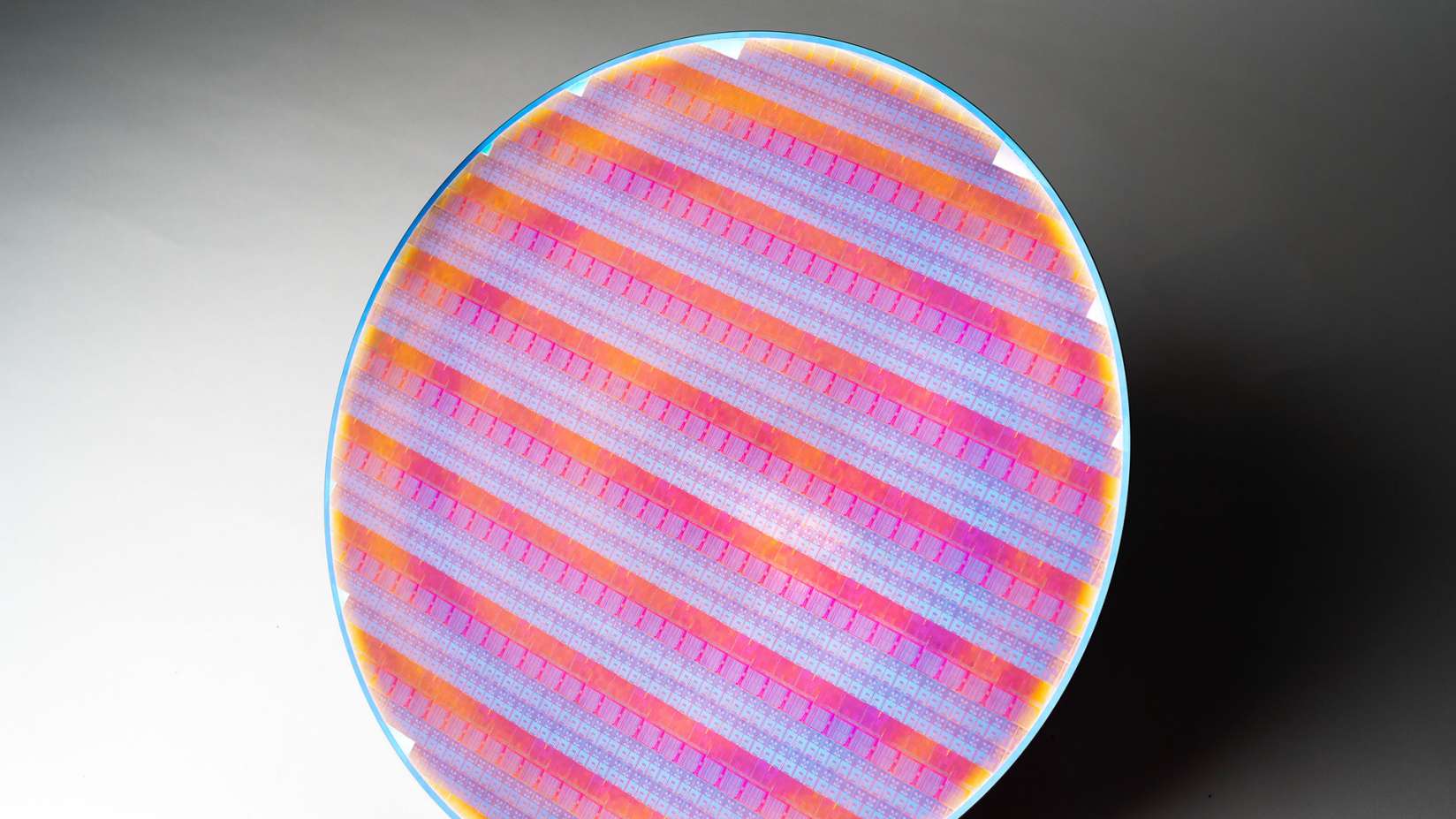

This paper presents a high-yielding backside power delivery (BPD) technology, PowerVia, implemented on Intel 4 finFET process. PowerVia more directly integrates power delivery to the transistor as compared to published buried power rail schemes, enabling additional wiring resources on front side for signal routing. A fabricated E-core with >90% cell utilization showed >30% platform voltage droop improvement and 6% frequency benefit compared to a similar design without PowerVia. Transistor performance, reliability, and fault isolation capability is detailed.

The problem of course is that TSMC is a fast follower. Not only are they a fast follower, TSMC has the support of the largest ecosystem known to the semiconductor industry.

At the 2024 North America Technology Symposium TSMC announced Super Power Rail for delivery in 2026 with the A16 node. The Super Power Rail, not unlike Intel PowerVia, enhances power efficiency and signal routing by dedicating front-side resources specifically for signals, aiming to improve logic density and performance for HPC applications. This is from the TSMC website:

TSMC A16™ technology is the next nanosheet-based technology featuring Super Power Rail, or SPR.

SPR is an innovative, best-in-class backside power delivery solution. It improves logic density and performance by dedicating front-side routing resource to signals. SPR also improves power delivery and reduces IR drop significantly. Most importantly, the novel backside contact scheme we developed preserves gate density, layout footprint, and device width flexibility, thus achieving best density and performance simultaneously, and we believe it is a first in the industry.

A16 is best suited for HPC products with complex signal routes and dense power delivery network, as they can benefit the most from backside power delivery. Compared with N2P, A16 offers 8%~10% speed improvement at the same Vdd, 15%~20% power reduction at the same speed, and 1.07~1.10X chip density.

Who Will Win?

It will be another battle of the technology titans: Intel PowerVia versus TSMC Super Power Rail. I have no doubt that Intel will be first with PowerVia on internal 18A products. I do believe that TSMC Super Power Rail will be the overall winner with foundry customers.

Which implementation will be best? We really won’t know until the chips fall but my guess is that they will be competitive. Intel should have the lead since they are designing PowerVia with specific chips in mind while TSMC’s Super Power Rail will have a broader application. I do believe, however, that in time the TSMC BSPD implementation will surpass Intel’s due to the driving force of the TSMC ecosystem.

Had Intel waited for chips to be in production before bragging about BSPD it would be a much different race, absolutely.

In 1996 former Intel CEO Andy Grove published the renowned book “Only the Paranoid Survive” which is an inside look at Grove’s management style and experiences at Intel. The key theme for me was that Andy believed in a healthy amount of paranoia to keep leaders vigilant, proactive, and prepared for the many disruptions of the semiconductor industry. Hopefully the new Intel CEO will have a healthy amount of paranoia.

Also Read:

Intel Presents the Final Frontier of Transistor Architecture at IEDM

Intel – Everyone’s Favourite Second Source?

Share this post via:

Comments

3 Replies to “What would you do if you were the CEO of Intel?”

You must register or log in to view/post comments.