In celebrating the 10th anniversary of SMIC, CEO David Wang ushers in a new era of China semiconductor manufacturing with triumphs versus promises. By triumphs David means profits, which SMIC saw for the first time in Q2 2010. The future looks even brighter for SMIC as the China semiconductor demand versus supply gap is an estimated $30B versus $3B.

SMIC is definitely positioned for growth with 10k+ people and $1.5B in 2010 revenue versus $1B in 2009. 2010 has been a banner year for the foundry industry with close to $30B in total revenues, which is approximately 10% of the $300B in total semiconductor revenue. Outsourcing from semiconductor IDM’s (fab-light strategy) continues to push foundry growth as well as mobile internet devices and emerging markets in China, India, and South America. It is interesting to note that Cadence CEO Lip-Bu Tan is on the SMIC board of directors. Lip-Bu’s Walden Venture Fund is heavily invested in the China fabless semiconductor market and he can spell cloud computing, so expect a strong move from Cadence in China.

Other interesting datapoints:

2010 Numbers

Electronics $1.36T +12%

Semi $300B +31.5%

EDA $5B +0%

CAPS $41.8B +90%

Fab Equip $28B +120%

SMIC Revenue

60% USA

30% China

10% Taiwan, UK, Israel, Korea

20% 90nm and below

Capacity Expansion Plans

8” 150k per month

12” 130/90nm 20k

12” 65/55nm 60k

12” 45/40nm 50k

12” 32/28nm 60k

Aart De Geus was the keynote speaker with an updated version of his: Systemic Collaboration: The New Smart Skill presentation. This presentation is looking more and more like an EDA360 pitch! I actually experienced déjà vu from conversations with EDA360 Chief Anarchist John Bruggeman!

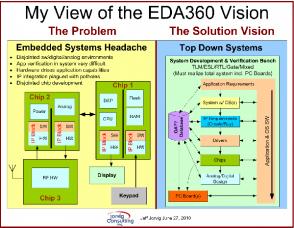

One of Aart’s slides highlighted the System, SoC, and Silicon Realization companies Synopsys had acquired over the years, an impressive list for sure. In fact, Synopsys dedicates 20%+ of revenue on M&A activity (inoraganic growth) versus 30%+ on R&D (organic growth). Unfortunately the Synopsys “Realization” strategy is FPGA based which will never work for bleeding edge semiconductor products that account for 90% of the silicon shipped in a year. The Cadence EDA360 vision is simulation/emulation based which is much better suited for “Realization”. Correct me if I’m wrong here Synopsys fans, this is just my impression/opinion.

The importance of IP re-use was also mentioned in regards to the increasing quality (yield) and time to market pressure the semiconductor industry faces. Better IP equals better yield, better yield equals time to market and better margins. As Aart says, the semiconductor design ecosystem is systemic. The results are not a SUM but a PRODUCT. If anywhere in the semiconductor design and manufacturing equation there is a zero, the results will be a bad wafer, die, chip, or electronic device, which supports the increasing importance of IP re-use.

I’m a Semiconductor IP person by experience and have blogged about it many times, and will do it again next week. Soft and hard IP cores continue to have a profound impact on SoC design. The trend I see is more soft IP versus hard, which presents a different type of qualification and integration challenge, but more on that next week.

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center