I visited Oasys Design Systems and talked to Craig Robbins, their VP sales. For the first time this year, Oasys has a theater presentations and demos of RealTime Designer which are open to anyone attending the show. In previous years, they have had suite demos for appropriately qualified potential customers but outside they have… Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More

Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More

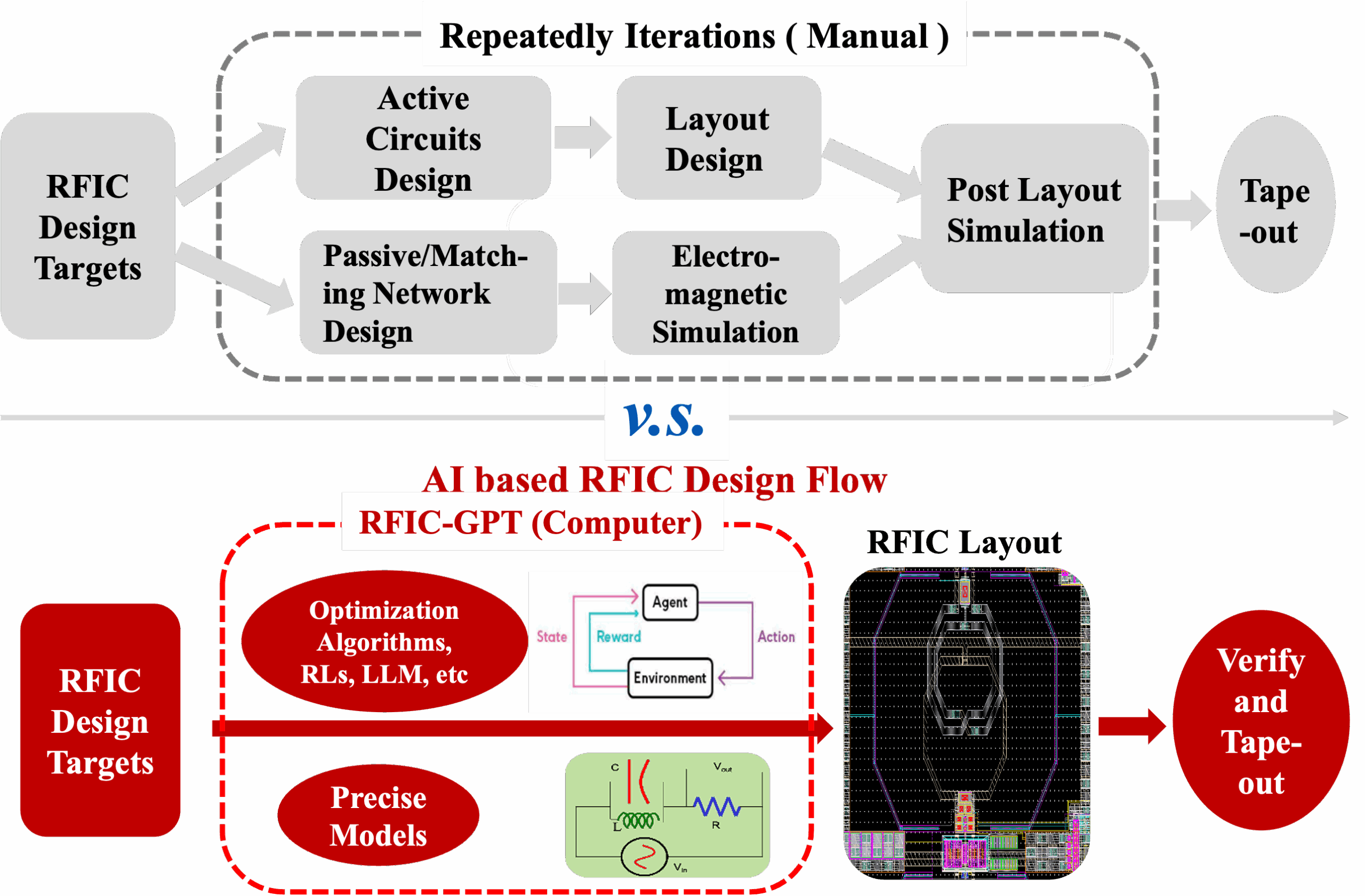

The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design AutomationBy Jason Liu, RFIC-GPT Inc. Radio frequency integrated…Read More

Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design AutomationBy Jason Liu, RFIC-GPT Inc. Radio frequency integrated…Read MoreTSMC Threater Presentation: Lorentz Solution!

Lorentz Solution presented at TSMC’s DAC 2012 Open Innovation Platform Theater. The presenter was Lorentz Sales Director, Tom Simon. He presented what Lorentz calls its Electromagnetic Design and Analysis Platform. One of the main points of the talk was the cooperative work that Lorentz does with TSMC.

Robustness, Reliability and Yield at DAC

On Wednesday at DAC I met with Bob Slee, distributor and Michael Siu, AE for MunEDA to get an update on what’s new. MunEDA has EDA software for:

- Schematic porting

- Nominal circuit analysis

- Nominal circuit optimization

- Statistical circuit analysis

- Statistical circuit optimization

- IP porting

- Circuit model generation

Methodics update at DAC

Fergus Slorach, CTO and Founder of Methodics met with me at DAC on Wednesday afternoon to provide an update on software configuration management for hardware designers.… Read More

Photo and Video Overview of DAC 2012

Sunday Night – you have to network at the EDAC kick-off party.… Read More

Analog FastSPICE update at DAC

Paul Estrada, COO of Berkeley DA met with me on the final day of DAC to provide an update. BDA coined the phrase Analog FastSPICE and have continued to dominate that market segment in the world of SPICE circuit simulators.… Read More

Microsoft Messes Up Mobile Even More…and Already Went Thermonuclear

Ed wrote recently about Microsoft going thermonuclear. I think that they already did. Ed wrote about Microsoft’s tablet announcement. The second announcement is a sort of follow up to my blog on what will happen to Nokia.

Two big announcements, the first one is that Microsoft is going to produce its own tablet computers (MiPads … Read More

AMS Simulation Update from Mentor Graphics at DAC

I met with Jay Madiraju of Mentor Graphics on Wednesday at DAC to get an update on their AMS simulation products. We worked together at Mentor back when Mach TA was being developed as a Fast SPICE circuit simulator.… Read More

FinFET Standard Cells at DAC

Rajiv Bhateja, Dhrumil Gandhi and Neal Carney met with me at DAC on Wednesday to give an update on what’s new in 2012 for Tela Innovations, a provider of lithography optimized IP and tools. This team has a rich history in EDA and IP from companies like: ARM, Artisan, Mentor Graphics and Silicon Compilers.… Read More

TSMC Theater Presentation: Apache

At the TSMC Theater Apache (don’t forget, now a subsidary of Ansys) talked about Emerging Challenges for Power, Signal and Reliability Verification on 3D-IC and Silicon Interposer Designs. The more I see about the costs and challenges of 20/22nm and below, the more I think that these 3D and 2.5D approaches are going to be … Read More

Quantum Computing Technologies and Challenges