Yes, it’s a pleasant surprise; it is Virtual Fabrication Platform, one of the new innovations in 2013. I was looking around for what kind of breakthrough technologies will be announced in DAC this year. And here I came across this new kind of innovative tool which can produce final virtual fabricated 3D structures after following… Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read MoreYou can tune a piano, but you can’t tune a cache without help

Once upon a time, designing a product with a first generation SoC on board, we were trying to use two different I/O peripherals simultaneously. Seemed simple enough, but things just flat out didn’t work. After days spent on RTFM (re-reading the fine manual), we found ourselves at the absolute last resort: ask our FAE.

After about… Read More

DAC lunch seminar: Better IP Test with IEEE P1687

What: DAC lunch seminar (register here)

When: June 5, 2013, 11:30am – 1:30pm

Where: At DAC in lovely Austin, TX

Dr. Martin Keim of Mentor Graphics will present this overview of the new the IEEE P1687 standard, called IJTAG for ‘internal’ JTAG.

If you are involved in IC test*, you’ve probably heard about IJTAG. If you … Read More

ARM SoC Hardening

Last year at DACI discovered a physical IP company called DXCorrthat competed against giant ARM. This year the company has selected a different direction, so I got caught up with Nirmalya Ghosh, the CEO to hear about the changes.

Nirmalya Ghosh, DXCorr

… Read More

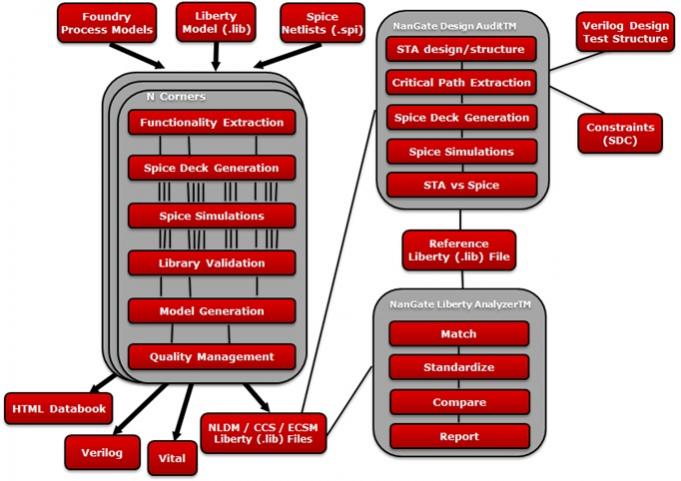

NanGate Launches Aggressive DAC Campaign: 50 Library Characterization Licenses for USD 50K

NanGate today announced a very aggressive “50-50 campaign”. Throughout June and July and in celebration of DAC 50th anniversary, NanGate will be offering 50 licenses of its Library Characterizer™ product for USD 50K for the first year. The offer applies to new customers as well as to existing customers that do not yet license the… Read More

TSMC ♥ Berkeley Design Automation

As I mentioned in BDA Takes on FinFET Based Memories with AFS Mega:

Is AFS Mega real? Of course it is, I’m an SRAM guy and I worked with BDA on this product so I know. But don’t take my word for it, stay tuned for endorsements from the top SRAM suppliers around the world.

Here is the first customer endorsement from the #1 foundry.… Read More

2013 semcionductor market forecast lowered to 6% from 7.5%

The global semiconductor market was weaker than expected in 1Q 2013, down 4.5% from 4Q 2012 according to WSTS. Much of the softnes was attributable to a major falloff in the PC market. According to International Data Corporation (IDC), 1Q 2013 PC shipments were down 15% from 4Q 2012 and down 14% from 1Q 2012. Other key end markets remained… Read More

Atrenta: Mentor/Spyglass Power Signoff…and a Book

Today Atrenta and Mentor announced that they were collaborating to enable accurate, signoff quality power estimation at the RTL for entire SoCs. The idea is to facilitate RTL power estimation for designs of over 50M gates running actual software loads over hundreds of millions of cycles, resulting in simulation datasets in the… Read More

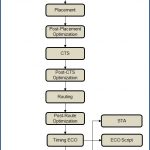

Efficient Handling of Timing ECOs

Today, in the design of any type of system on chip (SoC), timing closure is a major problem and it only gets worse with each new, and more advanced process technology. Timing closure is closely inter-leaved with power and clock design. The complexity of achieving closure rises sharply with increasing design density and advancing… Read More

Advanced Verification – HW/SW Emulation – SoC/ASIC Prototyping

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting