One of the places you will be able to find me at the Design Automation Conference (DAC) is on the speaker panel for a Monday Tutorial – Winning in Monte Carlo: Managing Simulations Under Variability and Reliability. Having worked closely with TSMC, GLOBALFOUNDRIES, Solido Design Automation, and some of the top fabless semiconductor… Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreSoC Optimization Using FPGA Prototyping

As an engineer I learn new concepts best by seeing a demonstration, in this case it was a demo of how to optimize SoC performance by using an ASIC prototyping debug process. SoC designers that use FPGAs to prototype their new ASIC often encounter debug issues, like:

- Limited observability of internal nets required for debug, maybe

5G – Reality or Fiction

Early in this week, I was reading news about Samsung announcing its breakthrough 5G mmWave technology. Well, this can bring fastest smart phone in the world which could enable several functions of day-to-day life and become revolutionary. The technology is not ready for commercial use, its building blocks seems to be working.… Read More

RTL Power Estimation at DAC

If you design with ARMCores and need to estimate dynamic power early in the flow, then consider what STMicroelectronics has done with their high performance, power-efficient subsystems. Anne Merlande is a Processor Micro Architecture technical expert, and will be presenting in Booth #1346 at DACon June 4th, 2:00PM. Her topic… Read More

IC Design with No Clocks Used in a SMART Card

My IC design career started at Intel with DRAM chips, so I’m very familiar with clockless design because we used self-timed techniques to get maximum performance. I remember blogging about an asynchronous design company called Tiempo back in 2010, while blogging at Chip Design Magazine. A few weeks ago there was a press … Read More

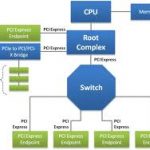

Are you going to the plug fest?

PCI Express 3.0 specification is 1000 pages long. Most of us, and most of the designers integrating PCIe gen-3 into their latest ASIC, FPGA or system will probably never read it completely, or even open it. In fact, they don’t need to read it completely, but they should care about one point, whether they buy an ASSP or a PCIe design IP:… Read More

Atrenta CEO on RTL Signoff

Most EDA companies sell tools into the main chip design and implementation flow such as simulation, synthesis, place & route, custom design and mask data prep. Atrenta is different. Nothing the company sells is in this main design flow. Instead, Atrenta focuses on pre-synthesis design analysis and optimization. Everything… Read More

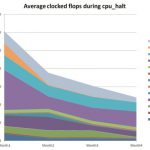

AMD Reduces Power by 20%

Steve Kommrusch of AMD wrote a white paper with Calypto on how AMD reduced power by 20% on the Jaguar SoC using Calypto’s PowerPro. Dan Nenni blogged about it on SemiWiki back in February here. And now, drumroll, Steve will present the story live and in person at DAC, on Monday June 3rd at 3pm and on Wednesday June 5th at 11am. This… Read More

Cadence Technical Sessions @ #50DAC (Free Food!)

Cadence is a DAC anchor, everyone will visit their booth, so lets look at their technical sessions and put our agendas together. Lets start with the breakfast/lunch sessions because Cadence usually puts out quite a spread, we all gotta eat and free food tastes even better:

Has “Timing Signoff Innovation” Become an Oxymoron? What… Read More

Tag it! Your customer will love using IP compliant with TSMC9000 IP Tag specification

We have seen last week in a first post how crucial was the IP qualification process (TSMC 9000) to increase the probability of successfully Tape Out a chip. Being able to discriminate between dangerous and safe IP is the first step of TSMC 9000 Quality process, IP tagging is the complementary step, almost as essential as the first … Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?