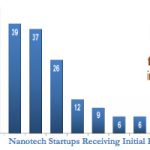

At the recent GSA Entrepreneurship Forumone of the panelists was Angel Orrantia of Innopartners who are trying a novel approach to funding startups in the semiconductor space and the surrounding ecosystem.

It seems things got started with an innovation center inside SK Hynix. Just in case you have forgotten, Hynix is the newish… Read More

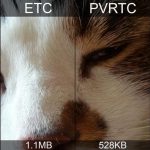

Solving the EDA tool fragmentation crisis