Last week was the TowerJazz Technology Fair 2013. TowerJazz is the fourth biggest foundry in the world after TSMC, GF and UMC. They have fabs in Newport Beach (the old Jazz, itself with roots in Rockwell), two in Israel (the old Tower, with roots in National Semiconductor) and one in Japan (acquired from Micron). The technology fair… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreAndroid Kit Kat Openly Preaching for DSP offloading

In fact KitKat advocates low-power always-on functionality, and this is essential for contextual-awareness. Always-on functionality is saving battery life, which seems to be weird at first: if your phone is always-on you would expect it to consume much power… But always-on goes together with screen-off (the screen is a high… Read More

Signoff Summit: The Fastest Path to Design Signoff

Cadence’s Signoff Summit will be held next week, November 21 at Cadence in San Jose.

This is the first of a series of all-day Signoff Summits from Cadence that focus on the multiple facets of design signoff. This first summit will include keynote addresses plus sessions covering the multiple solution components that comprise… Read More

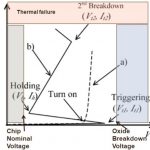

Full Chip ESD Sign-off – Necessary

As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More

Bringing EDA to India

Why do all three big EDA companies have user group meetings in India? The answer is to grow the EDA market in India because so many multi-national companies have engineers in India doing SoC, and IP design work. In my 35 years of IC design and EDA experience I’ve had the pleasure of working with and knowing many engineers and managers… Read More

ASICs for Bitcoin Mining!

One of the hottest areas for Application Specific Integrated Circuits today is Bitcoin mining. A good friend of mine has a son who is involved in a Bitcoin start-up so we have been discussing this at great length and I will share what I have learned thus far. Coincidently, my wife asked me about Bitcoin during our most recent walk down… Read More

A New IC Power Integrity Tool

In EDA we have come to expect that only small start-up companies create new tools, however a team at Cadencehas developed a new IC power integrity tool called Voltus from scratch. To learn more I spoke last week with KT Moore, a Group Director at Cadence. I’ve known KT for over a decade, and first met him when he was at Magma marketing… Read More

Is FD-SOI Really Faster, Cooler, Simpler?

I love the slogan associated with FD-SOI: the technology is supposed to be Faster, Cooler, Simpler. Does this slogan reflect the reality? Let’s start with Simpler. We (the semiconductor industry) have the perception that Silicon On Insulator (SOI) technology is something complex and exotic. Why? Because SOI has been used to … Read More

Xilinx Begins Shipping TSMC 20nm FPGAs!

Xilinx just announced the shipment of the first TSMC based 20 nm FPGAs, beating Altera to the punch yet again. Xilinx was also the first to ship TSMC 28nm FPGAs and will undoubtedly beat Altera to 14nm which could be the knockout punch we have all been waiting for. The Xilinx UltraScale is a new family of FPGAs that will use 20nm and 16nm… Read More

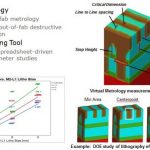

Semiconductor Fabrication Module Optimization

The growing process integration complexity at each technology node has increased development time and cost, and this trend looks to continue. There is a looming risk of delivering unrepeatable critical unit processes (or process modules) that would require revisiting development and manufacturing requalification or in … Read More

Solving the EDA tool fragmentation crisis